### INSTRUCTION MANUAL

# COMPUTER OF AVERAGE TRANSIENTS CAT SERIES 400

EXECUTIVE SALES OFFICE 202 Mamaroneck Avenue White Plains, New York

MANUFACTURING AND SERVICE 441 Washington Avenue North Haven, Connecticut

### Warranty

Equipment manufactured by TECHNICAL MEASUREMENT CORPORATION is fully guaranteed as to material and workmanship for a period of ONE YEAR. Auxiliary components supplied, but not manufactured by TMC are guaranteed by the respective manufacturers of the units. TECHNICAL MEASUREMENT CORPORATION reserves the right to perform warranty service operations either in its own factory, at an authorized repair station, or in the customer's installation. Our obligation under this Warranty is limited to repairing, or at our discretion replacing any defective parts thereof except fuses or batteries, without charge, if such defects occur in normal service, and provided the equipment or defective parts are returned, transportation charges prepaid, to the factory or other service point designated by TECHNICAL MEASUREMENT CORPORATION. Cathode-Ray tubes are guaranteed for a period of ONE YEAR. Cathode-Ray tubes are replaced at no cost for a period of NINETY DAYS and are prorated thereafter for an additional period of NINE MONTHS.

If any defect in material or workmanship is found which is covered by this Warranty, the following steps should be taken:

- Notify us, giving full particulars of the difficulty and including the model and serial number of the instrument in question. On receipt of this information, we will give you service information or shipping instructions.

- 2. If return of equipment is deemed necessary, shipping instructions will be forwarded together with an Authorized Return Certificate.

- 3. On receipt of shipping instructions, forward the apparatus to us prepaid, and we will immediately make repairs and adjustments at the factory and return the equipment to you prepaid.

- 4. If, during the Warranty period, it is disclosed by our examination that the fault has been caused by misuse or abnormal operating conditions, repairs will be billed at cost. In this case, an estimate of the cost will be submitted before the work is started.

Claims for damage in shipment should be filed promptly with the transportation company. All correspondence covering the instrument should specify the model and serial number and Authorized Return Certificate number.

TECHNICAL MEASUREMENT CORPORATION

441 WASHINGTON AVENUE

NORTH HAVEN, CONNECTICUT

| Section |                                                                                            |                                                                                                                                                                                                                              | Page                                                                         |  |  |

|---------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| - 1     | INTRODUCTION                                                                               |                                                                                                                                                                                                                              |                                                                              |  |  |

|         | 1.0<br>1.1<br>1.2<br>1.2.1<br>1.2.2                                                        | GENERAL  DESIGN FEATURES  SPECIFICATIONS  ELECTRICAL CHARACTERISTICS  PHYSICAL DIMENSIONS                                                                                                                                    | 1-1<br>1-1<br>1-3<br>1-3<br>1-4                                              |  |  |

| п       | OPERAT                                                                                     | ING INSTRUCTIONS                                                                                                                                                                                                             |                                                                              |  |  |

|         | 2.0<br>2.1<br>2.1.1<br>2.1.2<br>2.2                                                        | GENERAL  PREOPERATION INSPECTION  UNPACKING  VISUAL INSPECTION  CONTROLS, INDICATORS, AND                                                                                                                                    | 2-1<br>2-1<br>2-1<br>2-1                                                     |  |  |

|         | 2.2.1<br>2.2.2<br><b>2.3</b>                                                               | FRONT PANEL                                                                                                                                                                                                                  | 2–1<br>2–1<br>2–6                                                            |  |  |

|         | 2.3.1<br>2.3.2<br>2.3.3                                                                    | OPERATION                                                                                                                                                                                                                    | 2–9<br>2–9<br>2–9                                                            |  |  |

|         | 2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.6.1<br>2.4.6.2<br>2.4.6.3 | 600 CAT ACCESSORIES  CHECKOUT PROCEDURES  GENERAL  COMPUTER SECTION  MODULATOR SECTION  STIMULUS PULSE OPERATION  PRE ANALYSIS DELAY OPERATION  READOUT EQUIPMENT OPERATION  X-Y Plotter  Printer  Typewriter and Tape Punch | 2-10<br>2-13<br>2-13<br>2-13<br>2-14<br>2-14<br>2-14<br>2-14<br>2-15<br>2-15 |  |  |

| Ш       | THEORY                                                                                     | OF OPERATION                                                                                                                                                                                                                 |                                                                              |  |  |

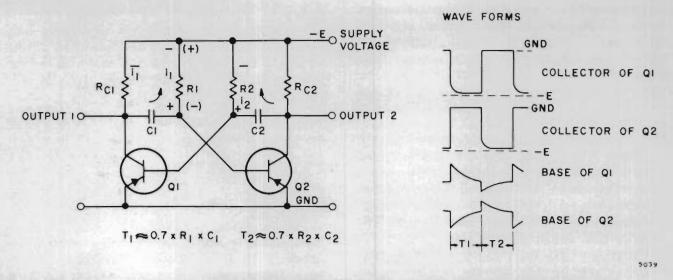

|         | 3.0<br>3.1<br>3.1.1<br>3.1.2<br>3.2<br>3.3                                                 | GENERAL BLOCK DIAGRAM DISCUSSION INPUT SECTION COMPUTER SECTION USE OF CIRCUIT DIAGRAMS INTRODUCTION TO THEORY OF OPERATION THE FREE RUNNING MULTIVIBRATOR                                                                   | 3-1<br>3-1<br>3-1<br>3-2<br>3-3                                              |  |  |

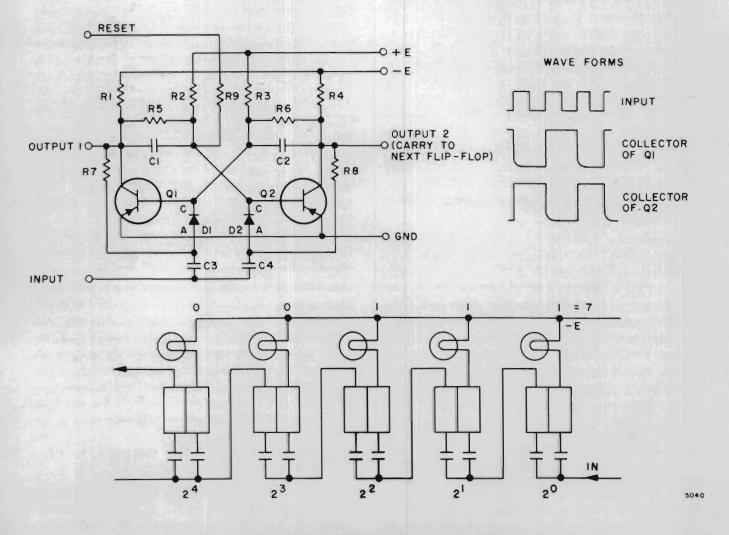

|         | 3.3.2                                                                                      | CIRCUIT THE BISTABLE MULTIVIBRATOR                                                                                                                                                                                           | 3–5                                                                          |  |  |

|         | J.U.Z                                                                                      | (FLIP-FLOP)                                                                                                                                                                                                                  | 3–5                                                                          |  |  |

| Section |                     |                                                                                | Page                 |

|---------|---------------------|--------------------------------------------------------------------------------|----------------------|

|         | 3.3.3               | THE BISTABLE MULTIVIBRATOR                                                     |                      |

|         | 0.0.4               | (TOGGLE)                                                                       | 3–7                  |

|         | 3.3.4               | THE MONOSTABLE MULTIVIBRATOR (ONE-SHOT)                                        | 3–7                  |

|         | 3.3.5               | THE SCHMITT TRIGGER                                                            | 3-7                  |

|         | 3.3.6               | THE NEGATIVE AND or POSITIVE                                                   |                      |

|         |                     | OR GATE                                                                        | 3-9                  |

|         | 3.3.7               | THE POSITIVE AND or NEGATIVE                                                   |                      |

|         |                     | OR GATE                                                                        | 3-9                  |

|         | 3.3.8               | THE DIODE GATE                                                                 | 3–9                  |

|         | 3.3.9               | DIODE-TRANSISTOR GATE, NAND GATE                                               | 2.0                  |

|         | 3.3.10              | (NOR GATE)                                                                     | 3-9<br>3-9           |

|         | 3.3.11              | THE EMITTER FOLLOWER                                                           | 3-11                 |

|         | 3.3.12              | THE PHASE SPLITTER-FREQUENCY                                                   | 0 11                 |

|         |                     | DOUBLER                                                                        | 3-11                 |

|         | 3.4                 | THEORY OF OPERATION                                                            | 3-11                 |

|         | 3.4.1               | INPUT SECTION                                                                  | 3-11                 |

|         | 3.4.1.1             | Modulator Circuit 8897                                                         | 3–11                 |

|         | 3.4.1.2             | Modulator By-Pass Circuits 8898                                                | 3-12                 |

|         | 3.4.1.3<br>3.4.1.4  | 1 KC Oscillator 9081                                                           | 3–12<br>3–12         |

|         | 3.4.1.4             | Delay Control Flip-Flop Circuit 8890                                           | 3-12                 |

|         | 3.4.1.6             | Trigger Generator 8999                                                         | 3-13                 |

|         | 3.4.1.7             | Modulator Gate Control Circuit 8895                                            | 3-14                 |

|         | 3.4.1.8             | 51.2 KC Oscillator and Shaper<br>Circuit 8888–2                                | 3–15                 |

|         | 3.4.1.9             | Scale of 16 Circuit 8889                                                       | 3-15                 |

|         | 3.4.1.10            | External Address Control Circuit 8998                                          | 3-16                 |

|         | 3.4.1.11            | Stimulus Pulse Generator Circuit 8892-2                                        | 3-16                 |

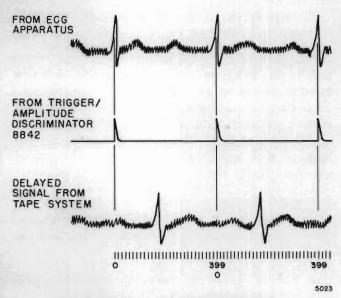

|         | 3.4.1.12            | Trigger/Amplitude Discriminator 8842                                           | 3–17                 |

|         | 3.4.2               | COMPUTER SECTION                                                               | 3-17                 |

|         | 3.4.2.1<br>3.4.2.2  | General Control Logic Circuit 8500                                             | 3–1 <i>7</i><br>3–18 |

|         | 3.4.2.3             | Auto Data Transfer Circuit 8501                                                | 3–18                 |

|         | 3.4.2.4             | Read Cycle Generator Circuit 8502                                              | 3-18                 |

|         | 3.4.2.5             | Write Cycle Circuit 8504                                                       | 3-18                 |

|         | 3.4.2.6             | Memory Current Generator 8503                                                  | 3-18                 |

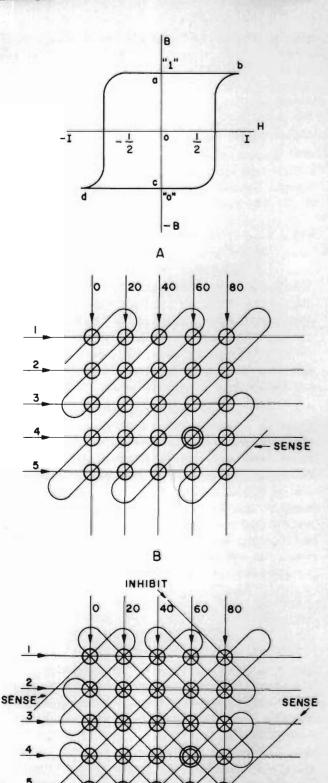

|         | 3.4.2.7             | Memory Operation                                                               | 3–19                 |

|         | 3.4.2.8             | Second Address Decade Circuits 8507-2                                          | 3–21<br>3–22         |

|         | 3.4.2.9<br>3.4.2.10 | 4 X 5 Memory Decoder Circuit 8506 Scale of Four/Memory Location Circuit 8508 . | 3-22                 |

|         | 3.4.2.11            | Arithmetic Decade Circuits 8512                                                | 3-23                 |

|         | 3.4.2.12            | Shift Logic Circuit 8511                                                       | 3-23                 |

|         | 3.4.2.13            | Sense and Inhibit Amplifier Circuits 8513                                      | 3-24                 |

|         | 3.4.2.14            | Digital-to-Analog Converter and Deflection                                     |                      |

|         | 0 1 0 1 -           | Amplifier Circuit 8509                                                         | 3-24                 |

|         | 3.4.2.15            | Selective Centering Circuit 8887                                               | 3-24                 |

|         | 3.4.2.16<br>3.4.3   | Filter Circuit Board B8833                                                     | 3-24<br>3-24         |

|         | 3.4.3.1             | Power Supply Filter and Rectifier                                              | 3-24                 |

|         | 0.1.0.1             | Circuit No. 2, 8496                                                            | 3-24                 |

|         | 3.4.3.2             | Power Supply Filter and Rectifier                                              |                      |

|         |                     | Circuit No. 1 8495                                                             | 3_25                 |

| Section |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|         | 3.4.3.3<br>3.4.3.4<br>3.4.3.5<br>3.4.3.6<br><b>3.5</b><br>3.5.1<br>3.5.2<br>3.5.3                                  | Voltage Regulator Circuit, —20, —12 8494. —4, +4, +20 Voltage Regulator 8493 Modulator Power Supply 8896 CRT High Voltage Power Supply 8492 OPERATION IN THE H AND D MODE GENERAL H MODE D MODE                                                                                                                                                                                                                                                                                                 | 3-25<br>3-25<br>3-25<br>3-25<br>3-26<br>3-26<br>3-26                                |

| IV      | MAINTE                                                                                                             | NANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                     |

|         | 4.0<br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.2<br>4.2.1<br>4.2.2<br>4.3<br>4.3.1 | INTERNAL ADJUSTMENTS  REFERENCE VOLTAGE (PLUS 4 VOLTS)  MEMORY CURRENT GENERATOR  ADJUSTMENT  CRT HORIZONTAL ALIGNMENT  DIGITAL-TO-ANALOG Y AXIS BALANCE  ALIGNMENT  DIGITAL-TO-ANALOG Y AXIS CENTER  AND SIZE ALIGNMENT  DIGITAL-TO-ANALOG X AXIS BALANCE  ALIGNMENT  TRIGGER/AMPLITUDE DISCRIMINATOR  LEVEL ADJUSTMENT  TROUBLE SHOOTING  GENERAL  POWER SUPPLY MALFUNCTIONS  SERVICE INSTRUCTIONS  RETURN OF THE COMPUTER OF AVERAGE  TRANSIENTS (CAT)  REPLACEMENT OF PLUG-IN CIRCUIT CARDS | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-3<br>4-11<br>4-11<br>4-11 |

| v       | 4.3.3                                                                                                              | SHIPPING INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4–12                                                                                |

| Mary.   | 5.0                                                                                                                | GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-1                                                                                 |

|         | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.7,1                                             | PROCEDURE  REMOVAL OF SIDE PANELS  REMOVAL OF PLUG-IN CIRCUIT CARDS  REPLACEMENT OF CATHODE RAY TUBE  (3RP-1)  REPLACEMENT OF —100 VOLT ZENER  DIODE (IN1375RA)  REPLACEMENT OF —20, —12, —4, +20, +4  VOLT POWER TRANSISTORS (1536, 1535)  REPLACEMENT OF NINE PIN CONNECTORS  (AMPHENOL 126—220)  FRONT PANEL COMPONENT REPLACEMENT  Reset Pushbutton (S7) and Toggle Switches                                                                                                                | 5-1<br>5-1<br>5-1<br>5-1<br>5-1<br>5-1<br>5-1<br>5-5                                |

|         | 5.1.7.2                                                                                                            | (\$4, \$5, \$6, \$8, \$9, \$11, \$12, \$13, \$14)<br>Indicator Lamps (\$L1, \$L2, \$L3, \$L4)                                                                                                                                                                                                                                                                                                                                                                                                   | 5-5<br>5-6                                                                          |

| Section |                |                                                                    | Page       |

|---------|----------------|--------------------------------------------------------------------|------------|

|         | 5.1.8<br>5.1.9 | EQUIPMENT SUPPLIED                                                 | 5-6<br>5-6 |

| VI      | APPLICA        | TIONS                                                              |            |

| 2       | 6.0<br>6.1     | GENERAL APPLICATIONS OF THE CAT USING                              | 6–1        |

|         |                | PROGRAM C                                                          | 6–1        |

|         | 6.1.1          | SIGNAL AVERAGE                                                     | 6-1        |

|         | 6.1.2          | CALIBRATION PROCEDURE                                              | 6-3        |

|         | 6.1.2.1        | General                                                            | 6-3        |

|         | 6.1.2.2        | Calibration of Analog Data                                         | 6-3        |

|         | 6.1.2.3        | Calibration of Digital Data                                        | 6-4        |

|         | 6.1.3          | AVERAGING APPLICATIONS                                             | 6-5        |

|         | 6.1.3.1        | General                                                            | 6-5        |

|         | 6.1.3.2        | Averaging of Evoked Responses                                      |            |

|         |                | From the Brain (EEG)                                               | 6-5        |

|         | 6.1.3.3        | Averaging of ECG Complexes                                         | 6-10       |

|         | 6.1.3.4        | Averaging NMR Signals                                              | 6-11       |

|         | 6.1.4          | SEQUENTIAL AMPLITUDE OR TIME INTERVAL COUNTING FUNCTIONS USING     |            |

|         |                | PROGRAM C                                                          | 6-12       |

|         | 6.1.4.1        | General                                                            | 6-12       |

|         | 6.1.4.2        | Stimulus Related Time Interval Sequence                            | 6-12       |

|         | 6.1.4.3        | Non-Stimulus Related Time Interval Sequence                        | 6-13       |

|         | 6.1.4.4        | Simulus Related Latency Sequence                                   | 6-14       |

|         | 6.1.4.5        | Non-Stimulus Related Dwell Time Sequence.                          | 6-15       |

|         | 6.1.4.6        | Non-Stimulus Related Amplitude Sequence                            | 6-17       |

|         | 6.2            | APPLICATIONS OF THE CAT USING                                      |            |

|         |                | PROGRAM H                                                          | 6-18       |

|         | 6.2.1          | NON-SEQUENTIAL PERIOD DISTRIBUTION CURVE                           | 6–18       |

|         | 6.2.2          | NON-SEQUENTIAL INTERNAL DISTRIBUTION                               | 0 .0       |

|         | 0.2.2          | CURVE                                                              | 6-19       |

|         | 6.3            | APPLICATIONS OF THE CAT USING PROGRAM D                            | 6–20       |

|         | 6.3.1          | NON-SEQUENTIAL STIMULUS RELATED LATENCY DISTRIBUTION CURVES        | 6-20       |

|         | 6.3.2          | NON-SEQUENTIAL NON-STIMULUS RELATED DWELL TIME DISTRIBUTION CURVES | 6-21       |

|         | 6.3.3          | NON-SEQUENTIAL NON-STIMULUS RELATED AMPLITUDE DISTRIBUTION CURVES  | 6-22       |

|         | 6.3.3.1        | Pulse Amplitude Distribution Curves                                | 6-22       |

|         | 6.3.3.2        | Amplitude Density Distribution Curves                              | 6-23       |

| VII     | CIRCUIT        | DIAGRAMS                                                           |            |

|         | GLOSSA         | RY OF TERMS                                                        |            |

|         | MALFUN         | CTION CHARTS                                                       |            |

# LIST OF ILLUSTRATIONS

| Figure     | Title                                                               | Page |

|------------|---------------------------------------------------------------------|------|

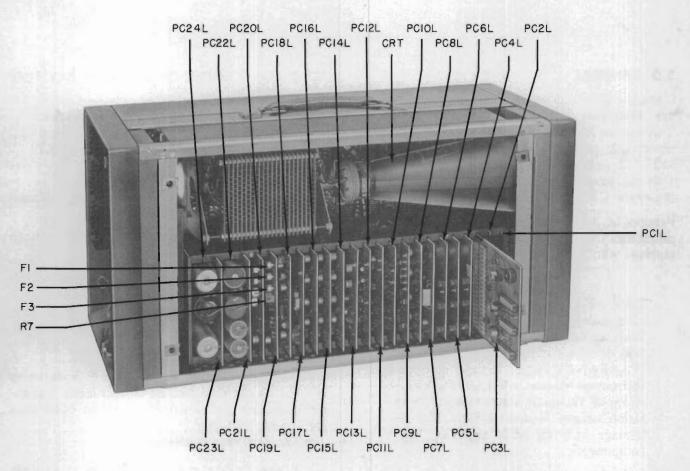

| 1-1        | Computer of Average Transients, Model 400B (CAT).                   | 1-0  |

| 2-1        | Computer of Average Transients, Models 400A, 400B                   |      |

|            | (CAT), Front View                                                   | 2-2  |

| 2-2        | Computer of Average Transients, Models 400, 400H                    |      |

|            | (CAT), Front View                                                   | 2–4  |

| 2–3        | Computer of Average Transients, Model 400B, Rear                    | 2-7  |

| 2 1        | View                                                                | 2-10 |

| 2-4<br>3-1 | Computer of Average Transients (CAT), Overall Block                 | 2-10 |

| 3-1        | Diagram                                                             | 3-0  |

| 3-2        | Free Running (Astable) Multivibrator, Circuit and                   |      |

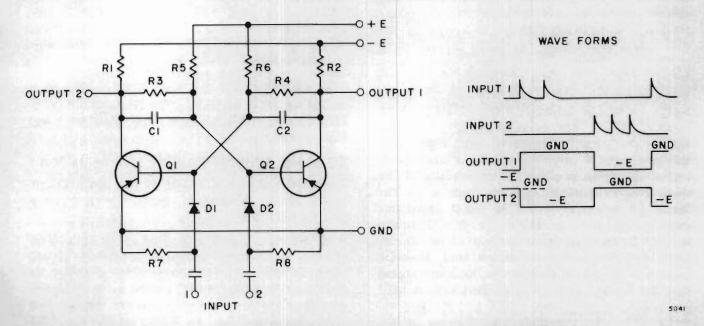

| • •        | Waveform Diagram                                                    | 3-4  |

| 3-3        | Bistable Multivibrator (Flip-Flop), Circuit and                     |      |

|            | Waveform Diagram                                                    | 3-4  |

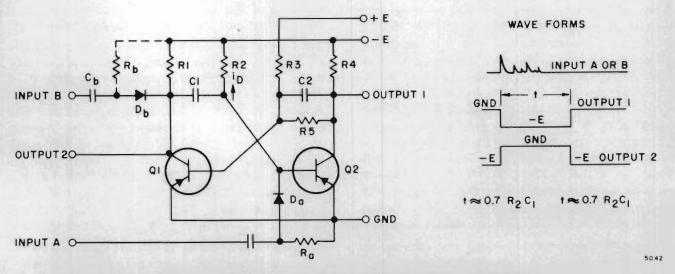

| 3-4        | Bistable Multivibrator (Toggle), Circuit and                        |      |

|            | Waveform Diagram                                                    | 3-6  |

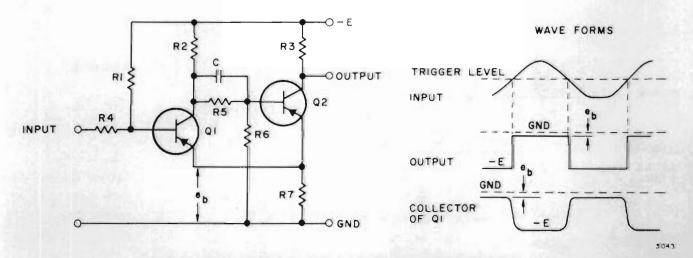

| 3-5        | Monostable Multivibrator (One-Shot), Circuit and                    |      |

|            | Waveform Diagram                                                    | 3-6  |

| 3–6        | Schmitt Trigger, Circuit and Waveform Diagram                       | 3–7  |

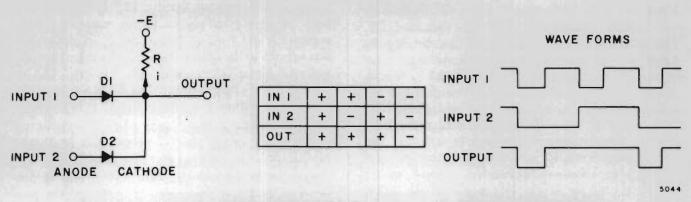

| 3–7        | Negative AND or Positive OR Gate, Circuit and                       |      |

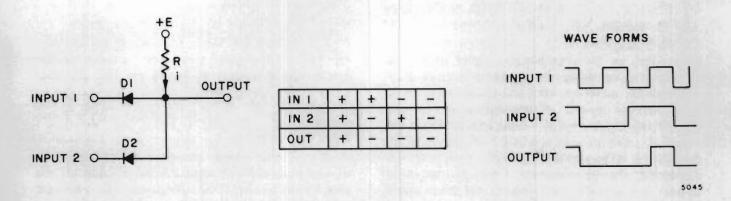

|            | Waveform Diagram                                                    | 3–8  |

| 3–8        | Positive AND or Negative OR Gate, Circuit and                       | 3-8  |

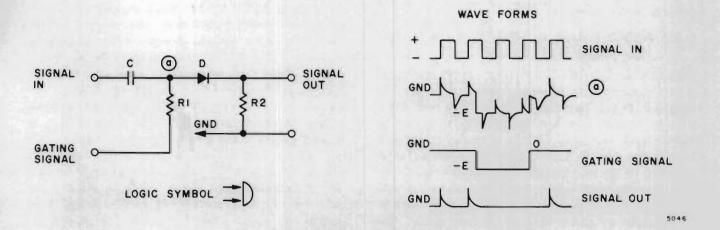

| 3-9        | Waveform Diagram                                                    | 3-8  |

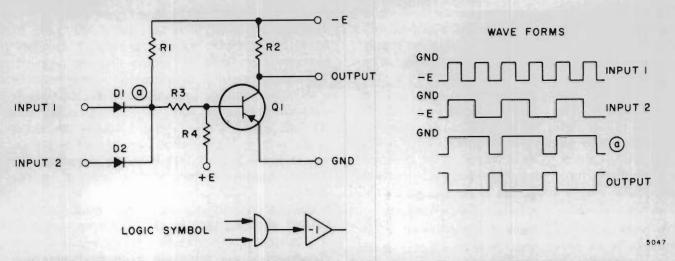

| 3-10       | Diode-Transistor Gate, NAND Gate (NOR Gate),                        | 3-0  |

| 0-10       | Circuit and Waveform Diagram                                        | 3-10 |

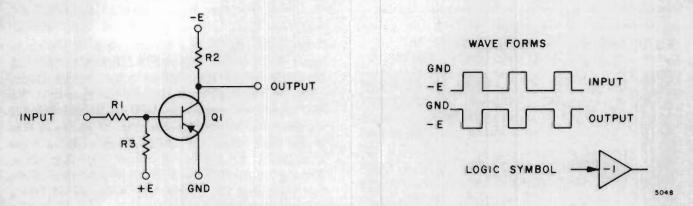

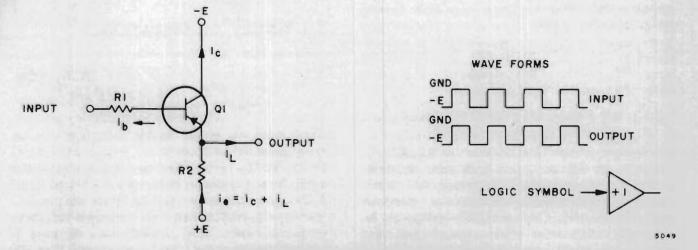

| 3-11       | Inverter, Circuit and Waveform Diagram                              | 3-10 |

| 3-12       | The Emitter Follower, Circuit and Waveform Diagram.                 | 3-10 |

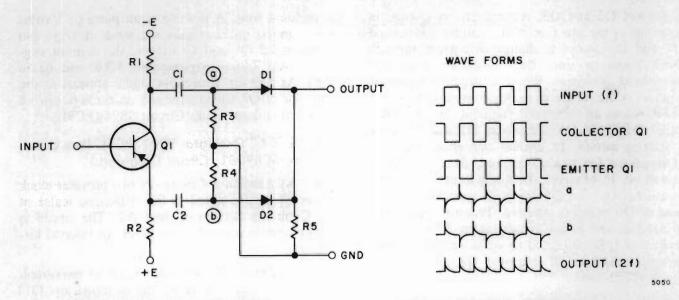

| 3-13       | Phase Splitter-Frequency Doubler, Circuit and                       |      |

|            | Waveform Diagram                                                    | 3-11 |

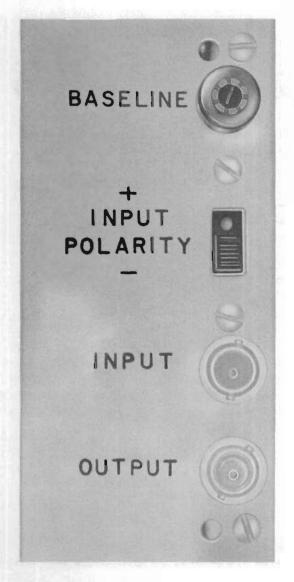

| 3-14       | Trigger/Amplitude Discriminator, 8842, Front View                   | 3-17 |

| 3-15       | Memory Core Operation Diagram                                       | 3-19 |

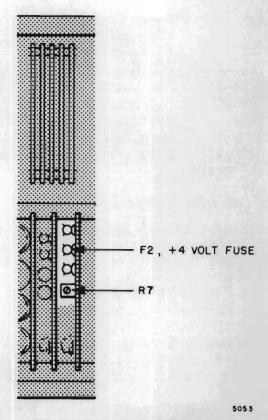

| 4-1        | Reference Voltage Adjustment Diagram                                | 4-1  |

| 4-2        | Memory Current Adjustment Diagram                                   | 4-2  |

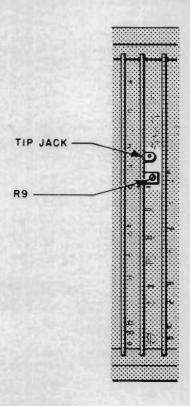

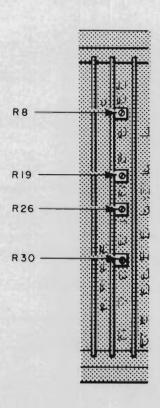

| 4-3        | CRT Alignment Diagram                                               | 4–2  |

| 5-1        | Computer of Average Transients, Model 400B (CAT),<br>Left Hand Side | 5-2  |

| 5-2        | Computer of Average Transients, Model 400B (CAT),                   | 3-2  |

| J-1        | Right Hand Side                                                     | 5-3  |

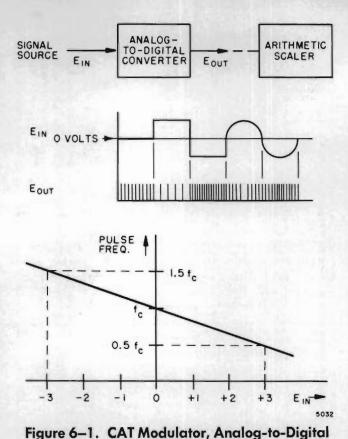

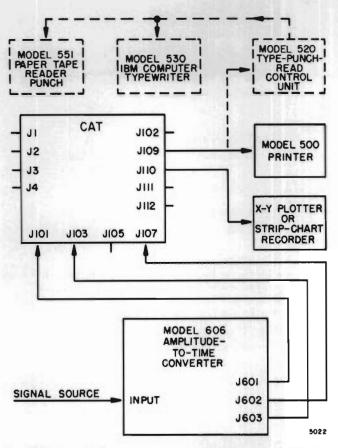

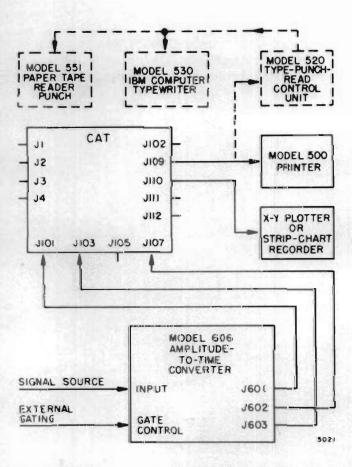

| 6-1        | CAT Modulator, Analog-to-Digital Converter                          | 6-2  |

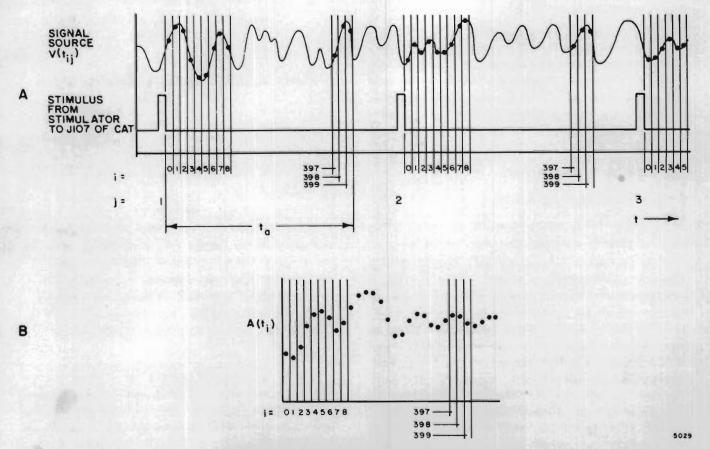

| 6-2        | CAT Averaging Process                                               | 6-2  |

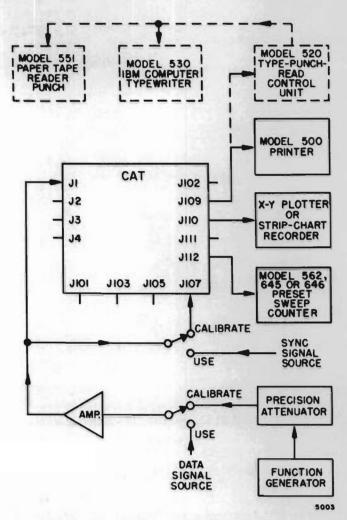

| 6-3        | Analog Calibration Procedure, Block Diagram                         | 6-3  |

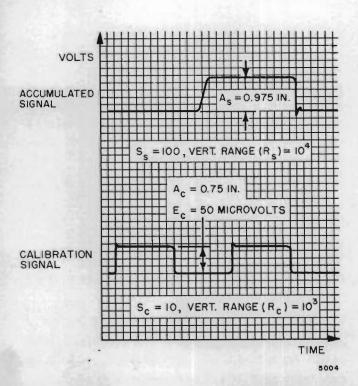

| 6-4        | Analog Calibration Procedure, Waveforms                             | 6-4  |

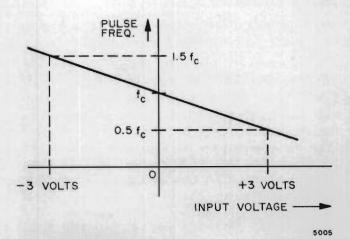

| 6-5        | Modulator Characteristics                                           | 6-4  |

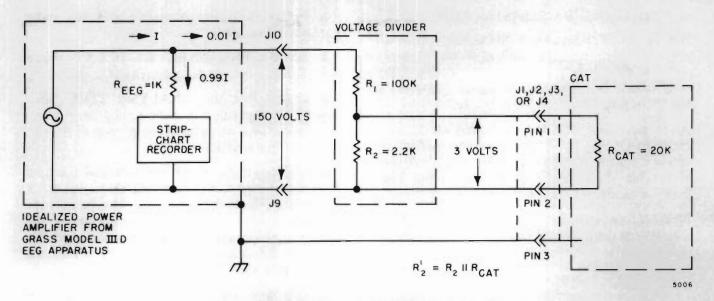

| 6-6        | EEG Interface Configuration, Circuit Diagram                        | 6-7  |

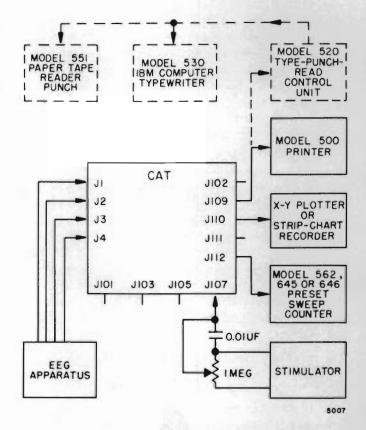

| 6–7        | External Stimulation in EEG Application, Block                      |      |

|            | Diagram with Interface Circuitry                                    | 6-7  |

#### LIST OF ILLUSTRATIONS

| Figure       | Title                                                                                                      | Page        |

|--------------|------------------------------------------------------------------------------------------------------------|-------------|

| 6-8<br>6-9   | External Stimulation in EEG Application, Waveforms. Internal Stimulation in EEG Application, Block Diagram | 6-8         |

| 6-10         | Internal Stimulation in EEG Application, Waveforms                                                         | 6-9<br>6-10 |

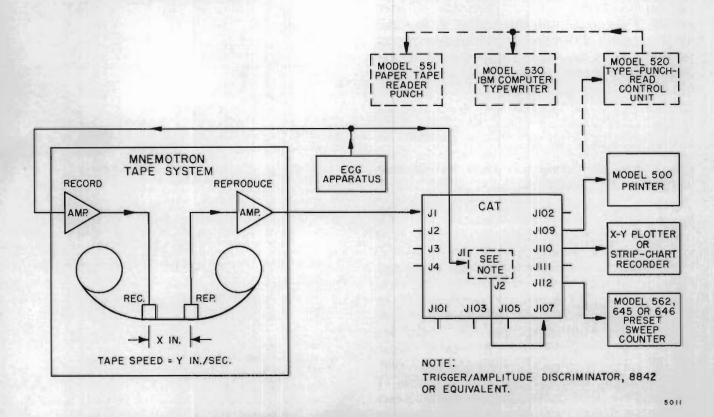

| 6-11<br>6-12 | Averaging of ECG Complexes, Waveforms ECG Application, Block Diagram                                       | 6-10        |

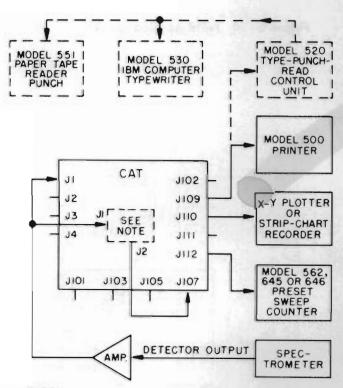

| 6-13         | NMR Application, Block Diagram                                                                             | 6-11        |

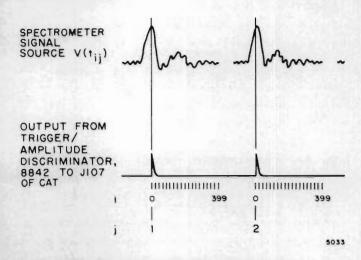

| 6-14         | NMR Application, Waveforms                                                                                 | 6-12        |

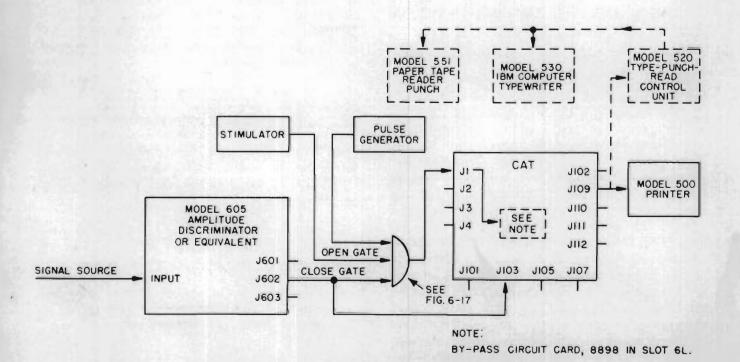

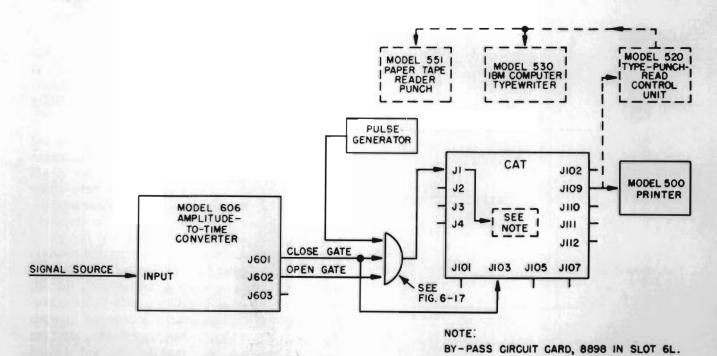

| 6–15         | Stimulus Related Time Interval Sequence, Block Diagram                                                     | 6–12        |

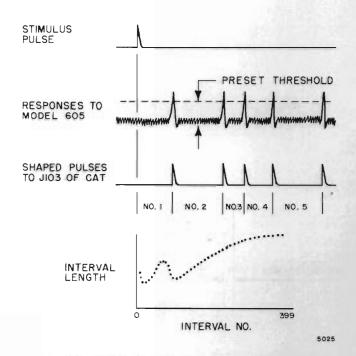

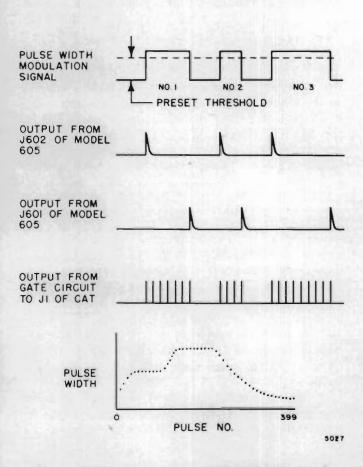

| 6–16         | Stimulus Related Time Interval Sequence, Waveforms                                                         | 6–13        |

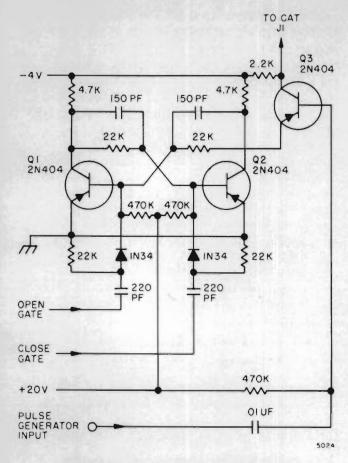

| 6-17         | Gate Circuit Diagram                                                                                       | 6-14        |

| 6-18         | Stimulus Related Latency Sequence, Block Diagram                                                           | 6-14        |

| 6-19         | Stimulus Related Latency Sequence, Waveforms                                                               | 6-15        |

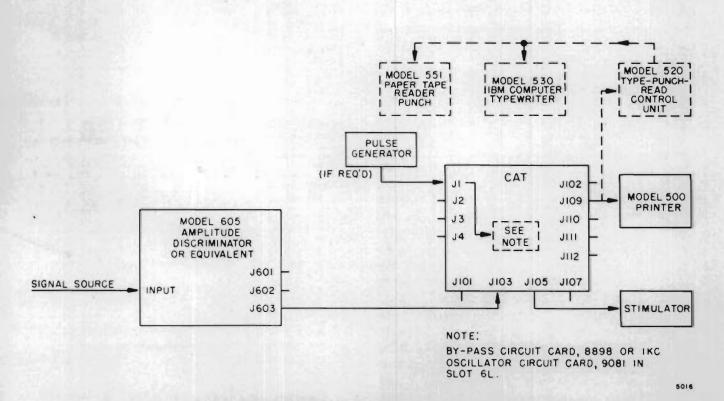

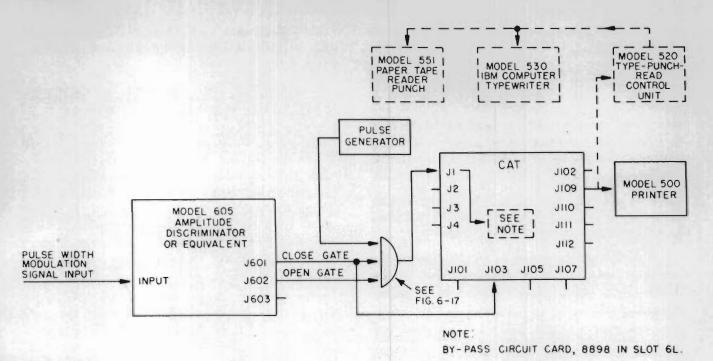

| 6–20         | Non-Stimulus Related Dwell Time Sequence, Block Diagram                                                    | 6–16        |

| 6–21         | Non-Stimulus Related Dwell Time Sequence,                                                                  |             |

|              | Waveforms                                                                                                  | 6–16        |

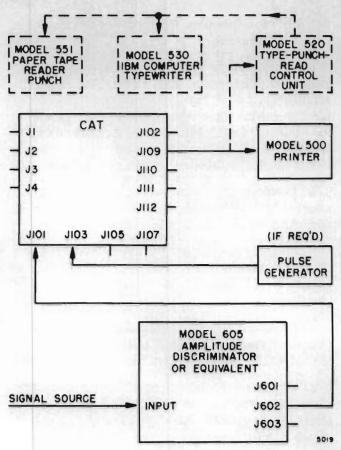

| 6–22         | Non-Stimulus Related Amplitude Sequence, Block Diagram                                                     | 6-17        |

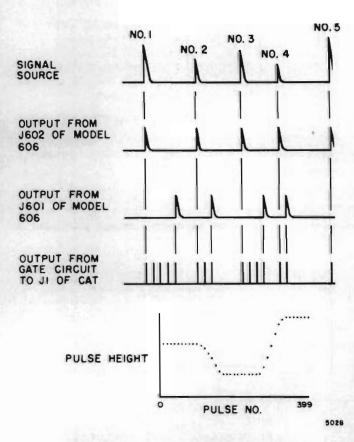

| 6–23         | Non-Stimulus Related Amplitude Sequence, Waveforms                                                         | 6–18        |

| 6-24         | Non-Sequential Period Distribution Curve, Block                                                            | 0-10        |

|              | Diagram                                                                                                    | 6–18        |

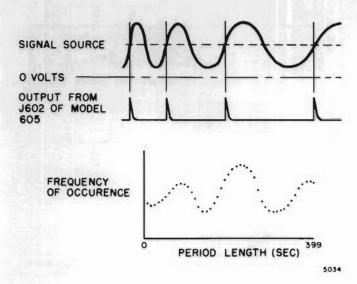

| 6–25         | Non-Sequential Period Distribution Curve, Waveforms                                                        | 6-19        |

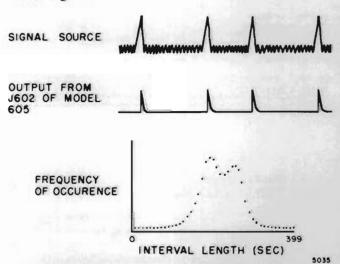

| 6-26         | Non-Sequential Interval Distribution Curve, Waveforms                                                      | 6-19        |

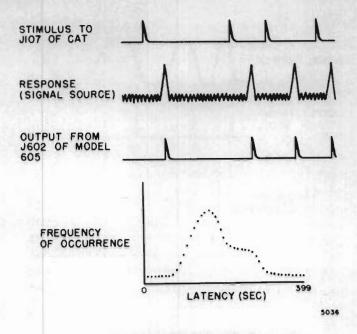

| 6–27         | Non-Sequential Stimulus Related Latency Distribution Curve, Block Diagrams                                 | 6–20        |

| 6–28         | Non-Sequential Stimulus Related Latency Distribution Curve, Waveforms                                      | 6-20        |

| 6–29         | Non-Sequential Non-Stimulus Related Dwell Time Distribution Curve, Block Diagram                           | 6-21        |

| 630          | Non-Sequential Non-Stimulus Related Dwell Time Distribution Curve, Waveforms                               | 6-21        |

| 6-31         | Model 606 Amplitude-to-Time Converter,                                                                     | 0-21        |

| ULSANI       | Block Diagram                                                                                              | 6–22        |

| 6–32         | Model 606 Amplitude-to-Time Converter, Internal Direct Pulse, Waveforms                                    | 6–22        |

| 6–33         | Non-Sequential Non-Stimulus Related Amplitude Distribution Curve, Direct Pulse Input, Block Diagram        | 6–23        |

| 6–34         | Non-Sequential Non-Stimulus Related Amplitude Distribution Curve, Direct Pulse Input, Waveforms            | 6-23        |

| 6–35         | Model 606 Amplitude-to-Time Converter, Internal Analog Waveforms                                           | 6-23        |

| 6–36         | Non-Sequential Non-Stimulus Related Amplitude Distribution Curve, External Control Input, Block Diagram    | 6-24        |

| 6–37         | Non-Sequential Non-Stimulus Related Amplitude Distribution Curve, External Control Input,                  | 0-24        |

|              | Waveforms                                                                                                  | 6-24        |

### LIST OF TABLES

| Figure Title                                  | Page     |

|-----------------------------------------------|----------|

| 2-1 J102 Remote Input Control and Scope Out   | tput 2–9 |

| 2-2 J104 Correlation Computer Connector (COI  |          |

| 2-3 J106 Correlation Computer Connector (COI  |          |

| 2-4 J109 Data Connector                       |          |

| 2-5 J110 Analog Connector                     |          |

| 2-6 J111 Remote Control Accessory Connector . |          |

| 2-7 J112 Accessory Connector for Sweep Cour   |          |

| Model 562                                     |          |

| 4-1 Voltage Supplies                          |          |

| 4-2 Trouble Shooting Chart                    |          |

| 5-1 Computer of Average Transients (CAT) Plug |          |

| Board List                                    | 5–4      |

| 5-2 Nine Pin Connector List                   |          |

| 5-3 Equipment Supplied                        |          |

| 5-4 Replaceable Parts List                    |          |

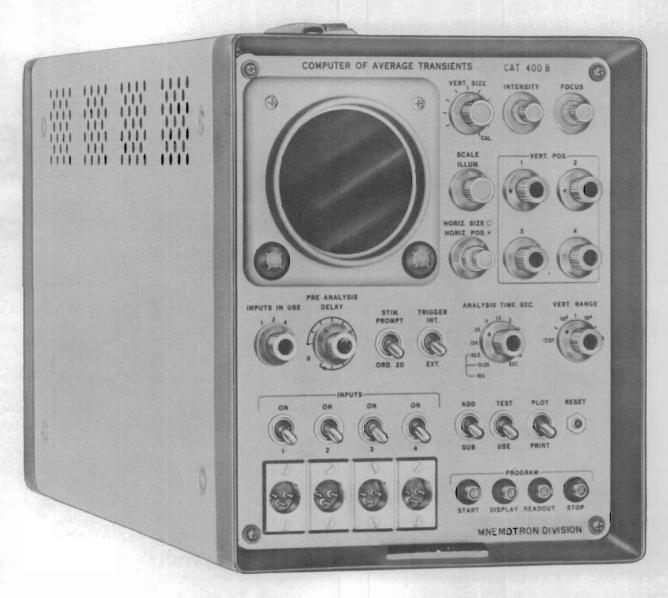

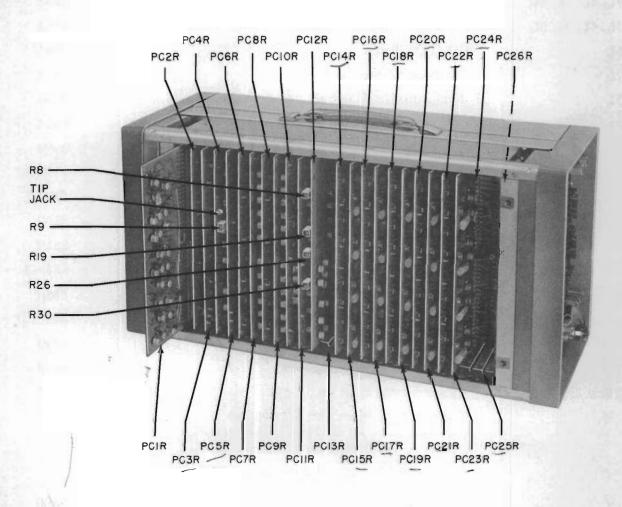

Figure 1-1. Computer of Average Transients, Model 400B (CAT).

## SECTION I

#### 1.0 GENERAL

The MNEMOTRON Computer of Average Transients (CAT) (see figure 1–1) is a special-purpose digital computer capable of isolating and evaluating small electrical responses masked by random background noise. This is done on-line, permitting the investigator to monitor and adjust parameters of the experiment while in progress. A summation (averaging) technique is automatically programmed which phase-locks the desired signal with relation to a known stimulus or reference pulse and sums successive responses. As a result, the signal under investigation will add arithmetically and the random background noise which sums out of phase will tend to cancel out.

The CAT incorporates its own analog-to-digital converters, thereby providing for the analysis of analog input signals on-line. The CAT outputs provide both digital and analog data for subsequent analysis. A three inch oscilloscope continuously displays the CAT memory contents during accumulate and display modes.

Digital output in binary-coded-decimal (BCD) form can be used with such MNEMOTRON units as the Model 500 Paper Tape Printer, the Model 510 Typewriter Drive Unit for IBM typewriter print-outs, or the Model 520 Type-Punch-Read Control Unit for punch-read devices.

An analog output of 0 to 100 millivolts is provided for use with strip-chart recorders and X-Y plotters.

#### 1.1 DESIGN FEATURES

PORTABILITY—The Computer of Average Transients is designed for use within the immediate area of experimentation. The unit, weighing 38 pounds, and occupying a space 8-1/2 X 10-1/2 X 22 inches can easily be transported to any location for a variety of applications.

- FLEXIBILITY—Experimental procedures incorporating the CAT may be modified by the operator at any time during the investigation. This provides considerable flexibility in its operation and requires no special programming techniques.

- EXTERNAL CONNECTIONS—External connections on the instrument are available to permit operation from remote equipment. Provisions are also available for the use of external stimuli for reference pulses as well as internal stimuli capable of activating remote ancillary instrumentation.

- MEMORY CAPABILITY—The CAT is composed of a magnetic core system in which the data are stored in BCD form. There are 400 memory addresses, each capable of storing 20 binary digits (bits) representing a count of  $10^5-1$  in decimal form. Total memory consists of 8000 cores. Memory addresses capable of storing 24 bits  $(10^6-1)$  are also available.

- ADD OR SUBTRACT FEATURE—Memory information can be stored in either an ADD or SUBTRACT mode. This feature permits a response signal to be added or subtracted from the data already existing in the CAT memory.

- OSCILLOSCOPE DISPLAY—A 3" High-Resolution CRT integral to the unit is provided to monitor the data accumulated in the memory system. It gives an analog display of the stored information and can easily be adjusted for signal delineation. Provisions are available in the Model 400B for slaved operation of external oscilloscope equipment.

- ADDRESS IDENTIFICATION—Alternate groups of 10 addresses are intensified for easier identification of data location within the CAT memory.

INPUT ADAPTABILITY—One, two, or four input selections can be obtained which permit processing of individual or up to four simultaneous or consecutive response signals. Outputs clearly define each signal and the CRT simultaneously displays the separate and distinct responses.

TRANSISTORIZATION—The instrument is completely transistorized. All components are mounted on printed circuit boards to insure reliable operation under rugged environmental conditions.

PLUG-IN CARDS—Plug-in circuit board cards are used throughout the unit, providing simple replacement when necessary. Extension cards are provided for testing plug-in cards while the CAT is operating.

ACCESSORY INTEGRATION—The CAT Series 600 Accessories have been designed for use with the MNEMOTRON Computer of Average Transients. They provide the CAT with additional features which greatly expand its capabilities and operation. The following list outlines the current Series 600 Accessories with a brief description of their functions.

#### SERIES 600 ACCESSORIES

| Model No. | Name                                 | Function                                                                                                                                                                                                |

|-----------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 600       | CAT ACCESSORY CABINET                | Houses Series 600 Accessories. Contains internal power supply for all connected accessories. Provides for all necessary connections to CAT and ancillary equipment.                                     |

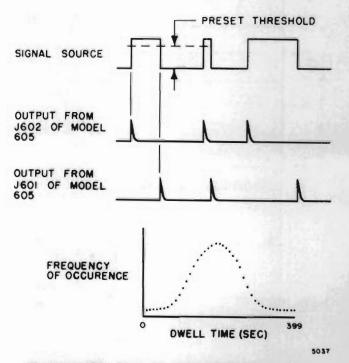

| 605       | AMPLITUDE DISCRIMINATOR              | Contains adjustable baseline voltage selector.<br>Transmits a pulse to CAT when preselected baseline<br>amplitude is exceeded, followed by a pulse when<br>voltage drops below preset amplitude.        |

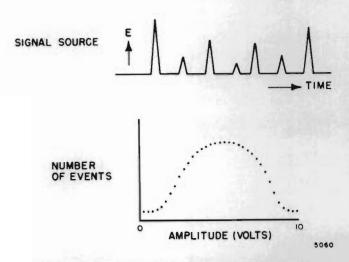

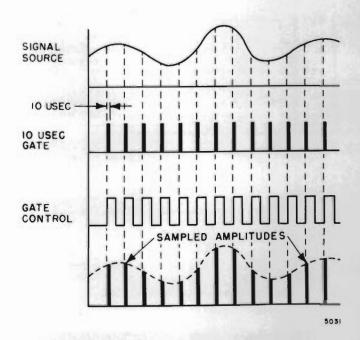

| 606       | AMPLITUDE-TO-TIME<br>CONVERTER       | Sorts input pulses from zero to ten volts into 400 memory addresses. The CAT receives this programmed data and deposits one count into an address proportional to the amplitude of the input signal.    |

| 620       | READOUT CONTROL (retrace suppressor) | Eliminates visible traces on associated X-Y plotters when more than one trace is utilized.                                                                                                              |

| 635       | MEMORY RESET UNIT                    | Permits manual reset of any memory quarter in the CAT.                                                                                                                                                  |

| 645       | PRESET SWEEP COUNTER                 | Permits manual selection of number of CAT analysis sweeps and terminates operation when preset number has been reached.  Electromechanically displays sweep numbers downward from preselection to 0000. |

| 646       | PRESET SWEEP COUNTER                 | Permits manual selection of number of CAT analysis sweeps and terminates operation when preset number has been reached.  Electronically displays sweep numbers upward from zero to preselected number.  |

CABLES

#### 3-BNC Cables

(Used only with Models 605 & 606) (Used only with Models 605 & 606) (Used only with Model 606) 1-Cable 1-Cable

1-Cable

#### Connections from:

J601 to CAT J101 J602 to CAT J107 J603 to CAT J103 Connections from J103 to CAT J110, J111, J112 Connections from J109A to CAT J109 3-wire connection to AC power

#### 1.2 SPECIFICATIONS

#### 1.2.1 ELECTRICAL CHARACTERISTICS

#### **INPUTS**

Connectors

Impedance

Signal (for linear operation)

Maximum

Common Mode Voltage

Remote Controls

#### **OUTPUTS**

**Digital**

Analog

Stimulus Pulse

Monitor

Readout Speeds

#### OPERATING CHARACTERISTICS

Addresses (Analysis Points)

Analysis Time

Memory Capacity

Delay (between stimulus and response analysis)

Storage Cycle Time

External Address Advance Rate

Modulator Linearity

(Analog to Digital Converter)

Modulator Frequencies

(Analog to Digital Converter)

Maximum Input Rate to Modulators

4 Signals to pin 1 and 2

Chassis ground—pin 3

(pin 1 negative with respect to pin 2 causes

reduction of modulator frequency)

20,000 ohms

Plus or minus 3 volts (6 volts peak to peak)

50 volts internally clipped to approximately plus or

minus 4 volts

300 volts maximum

For start, display, readout, stop, reset function, and

external control of input modulators

binary coded decimal (address and arithmetic)

0 to plus 100 millivolts (for X and Y data)

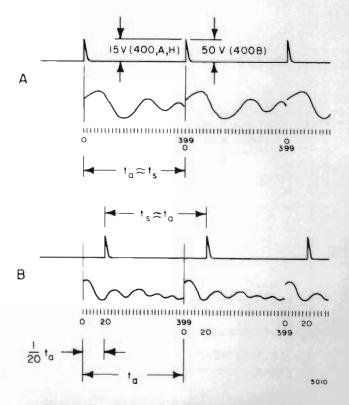

plus 50 volts-Model 400B

plus 15 volts-Models 400, A, H

(10 millisecond duration, approximately 1 micro-

second risetime, 20,000 ohms impedance)

3-inch Cathode Ray Tube

0.8, 4, 16, 40 or 400 seconds-Model 400, H

12 to 120 seconds (continuously variable)—Models

400A, B

400

31.25, 62.5, 125, 250 milliseconds, 0.5, 1.0, 2, 4,

8, 16 seconds—Model 400B

62.5, 125, 250 milliseconds, 0.5, 1.0, 2, 4, 8, 16, 32

seconds-Models 400, A, H

(Can be varied externally from 20 milliseconds to

any desired value)

105-1 counts per address

106-1 counts per address (available on request)

100 microseconds or approximately 0.1 to 10 sec-

onds (variable)

36 microseconds

20,000 addresses per second

plus or minus 0.5 per cent of full scale

50, 100, 250, 500 KC

2500 cps

#### Section I

#### INTRODUCTION

#### PROGRAM SWITCH C POSITION

**External Trigger**

Rise Time

Minimum Input Voltage

Maximum Repetition Rate

External Address Advance

Rise Time

Minimum Input Voltage

Maximum Repetition Rate

PROGRAM SWITCH H POSITION

Maximum Address Advance Rate

Maximum Address Reset Rate

PROGRAM SWITCH D POSITION

Maximum Address Advance Rate

Maximum External Trigger Rate

Maximum Address Reset Rate

POWER REQUIREMENTS

Voltage

Frequency

Power

DC Operation

1.2.2 PHYSICAL DIMENSIONS

Height

Width

Length

Weight

10 microseconds

plus 2 volts (minus 2 volts on Model CAT 400)

50 pps

less than 10 microseconds

plus 1 volt

20,000 pps

800,000 pps

10,000 pps

800,000 pps

10,000 pps

10,000 pps

100, 115, 200, 215 or 230 volts ac

50 to 400 cps

30 watts (approximately)

DC to AC converter available

10-1/2 inches

8-1/2 inches

22 inches

38 pounds (approximately)

# SECTION II OPERATING INSTRUCTIONS

#### 2.0 GENERAL

This section contains operating and checkout procedures for the Computer of Average Transients (CAT). Paragraph 2.2 and figures 2–1, 2–2, 2–3, detail all controls, indicators and connectors.

#### 2.1 PREOPERATION INSPECTION

#### 2.1.1 UNPACKING

The CAT is carefully packed into a custom-fitted shipping container at the factory. No special instructions are required to unpack the unit, but extreme caution should be taken not to damage the instrument. Containers should be stored until checkout has been completed in case reshipment is necessary.

#### 2.1.2 VISUAL INSPECTION

After the equipment has been unpacked, perform a thorough visual inspection. Make certain that all knobs and connectors are secure and that there is no external damage.

Loosen four fasteners on each side cover. Without removing cards, thoroughly inspect exposed wiring and plug-in cards for obvious damage. Should front panel knobs appear loose, allen wrenches will be found on left-hand side under CRT.

#### NOTE

If necessary to remove plug-in cards, do not remove more than one card at a time without marking so that card can be returned to proper position.

#### CAUTION

Do not remove or replace any cards with power on. Before removal make certain POWER switch is at OFF position.

### 2.2 CONTROLS, INDICATORS, AND CONNECTORS

The following paragraphs outline the controls, indicators, and connectors for the Computer of Average Transients (CAT).

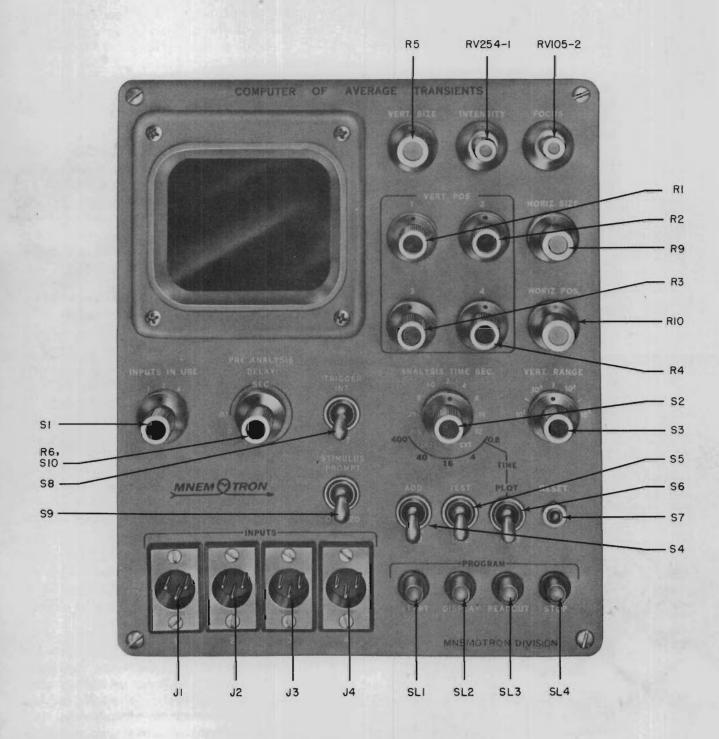

2.2.1 FRONT PANEL (See figures 2-1, 2-2.)

VERT. SIZE Control—The VERT. R5 SIZE control is a vernier which covers the range between two adjacent positions of the VERT. RANGE (S3) switch. In the maximum clockwise position of the VERT. SIZE control the full scale values as indicated by the VERT. RANGE switch apply. This position should be used at all times when quantitative amplitude data are to be derived from the displayed trace either by visual inspection or photography. The scale on this control is not calibrated; it is intended to aid the experimenter to find a given setting after the position has been altered. Scale gradations provided only on Models 400A, 400B.

RV254-1 INTENSITY Control—Dims or brightens CRT display. Proper adjustment of this control will provide for intensity modulation of every 10 addresses for detailed visual inspection of trace on CRT. Alternate addresses are brightened when control is rotated counterclockwise.

RV105-2 FOCUS Control—Sharpens focus of CRT display.

CRT SCALE ILLUM. Control—Dims or brightens scale graticules on CRT window. Provided only on Models 400A, 400B.

R1, R2, VERT. POS. Controls—The VERT.

R3, R4

POS. controls (4 potentiometers) determine the vertical location of subgroups of the memory on the CRT display.

With the INPUTS IN USE switch on 4, each control positions the trace recorded from the input carrying the same number. At two inputs in use, control 1 positions the trace recorded from input 1, and control 3 the one recorded from input 2. At one input in use, control 1

positions the entire trace.

Figure 2–1. Computer of Average Transients, Models 400A, 400B (CAT), Front View.

2-2

**S9**

S8

S2

R9 HORIZ. SIZE Control—Controls width of traces on CRT display.

R10 HORIZ. POS. Control—Positions all traces horizontally.

S1 INPUTS IN USE Selector Switch—The INPUTS IN USE switch selects the number of subgroups of the memory and, therefore, the number of inputs which may be used to receive input information.

In the 1 position only signals supplied to input 1 will be accumulated. The whole memory is used to store the information.

In the 2 position the memory is divided into two subgroups of 200 addresses each. Information is received through inputs 1 and 2 only on a time shared basis; i.e., the signal from input 1 only is routed to zero address of the memory for a predetermined period of time (selected by the ANALYSIS TIME switch), then the signal from input 2 is routed to address 200 of the memory for the same period of time, the further sequence being 1, 201; 2, 202; 3, 303; etc. . . .

In the 4 position the memory is divided into four subgroups and signal information is received through all four inputs again on a time sharing basis. The sequence is:

Time Interval  $t_1 = t_2 = t_3 = t_4 = t_5 = t_6 = t_7 = t_8 = t_9$

| Input 1 | 0 |     |     | 100 | 1 |     |     | 77  | 2 |

|---------|---|-----|-----|-----|---|-----|-----|-----|---|

| Input 2 |   | 100 |     | -   |   | 101 |     |     |   |

| Input 3 |   |     | 200 |     |   | 1   | 201 |     |   |

| Input 4 |   |     |     | 300 |   | 100 |     | 301 |   |

Addresses

$t_n = \frac{ta}{400}$  where  $t_n =$  time interval or dwell time, and ta = analysis time as set on front panel.

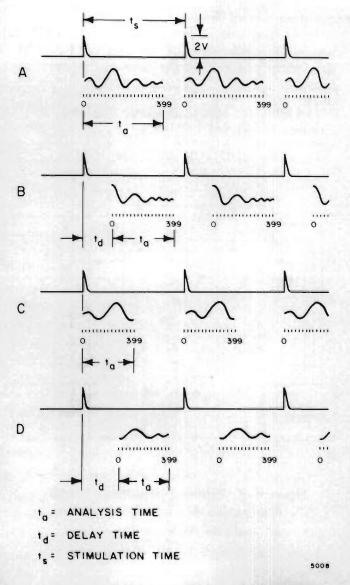

R6/S10 PRE ANALYSIS DELAY Control— The PRE ANALYSIS DELAY control provides a delay between the application of a trigger pulse and the start of the analysis sweep. In its maximum counter-clockwise (detent) position there is no delay between the application of a trigger pulse and the start of the analysis sweep. Moved out of the detent position a minimum delay between receiving a trigger pulse and the start of the analysis sweep of 100 milliseconds is provided which may be continuously increased to approximately 10 seconds at maximum clockwise position of the control. The scale on this control is not related to the actual delay time but is only provided to aid the experimenter to repeat a previously used setting. (The trigger pulse may be either internally or externally generated.)

STIMULUS Switch—The STIMULUS switch provides 50 volt positive pulse at J105 on the rear panel when the CAT is in the accumulate mode, START switch (SL1) lit. For the other CAT 400 models this pulse is plus 15 volts. If this switch is in the PROMPT position a pulse will occur at the time of the start of each analysis sweep. In the ORD. 20 position this pulse is generated when the sweep passes through address 20.

TRIGGER Switch—With the TRIGGER switch in the EXT. position, an external trigger pulse of at least plus 2 volts applied to J107 on the rear panel is required to actually start on analysis sweep. At the end of a sweep the CAT will return to zero address and wait for a new trigger pulse to initiate another sweep. START pushbutton (SL1) must be depressed before an analysis sweep can be started. Model 400 requires a minus 2 volt trigger pulse.

On the INT. position a sweep is started 50 microseconds after depressing the START pushbutton (SL1) and from thereon 100 microseconds after completion of each sweep.

ANALYSIS TIME SEC. Switch—The ANALYSIS TIME switch determines the period of time, in seconds or milliseconds, allocated for each complete analysis sweep of 400 addresses and, consequently, the time per address is the ANALYSIS TIME divided by 400. Regardless of the position of the INPUTS IN USE switch (S1), the time per

Figure 2–2. Computer of Average Transients, Models 400, 400 H (CAT), Front View.

1005

\$5

analysis sweep is always as determined by the position of S2. When this control is in the EXT. position the addresses may be advanced at any desired rate up to 20,000 addresses per second (ANALYSIS TIME of 20 milliseconds) by supplying external pulses to J103.

The earlier Model CAT 400 also has a plot time selector operated by the same control. In this case, the knob has one blue dot and one red dot. The blue dot should be in line with the desired analysis time of the inner (white) nomenclature. The red dot should be lined up with a suitable plotting time on the outer (red) nomenclature when the CAT is in readout mode. For Models CAT 400A and B see Rear Panel, PLOT TIME control (R102, figure 2-3).

**S**3 VERT. RANGE Switch—The VERT. RANGE switch determines the full scale vertical range of the analog output as displayed on the CRT. The line beyond each power of ten setting represents the next higher setting divided by a factor of 3. (Thus a full scale display represents 333, 3333, or 33,333 counts in one of these intermediate positions.) Only the three most significant decades are displayed. The setting of this switch does not alter the capacity of the memory, it merely affects the display on the CRT and the analog voltage output of the CAT.

J1, J2, Input Connectors—The Inputs are di-J3, J4 rectly coupled to the modulators. No amplification is provided. They are isolated from ground and from each other so that signals floating at different dc levels may be connected. The signals should be connected to pins 1 and 2. Pin 3 is connected to chassis ground and is used to ground the shield of the input cable if a shielded cable is employed.

> The input impedance is approximately 20,000 ohms. A maximum signal of plus or minus 3 volts (6 volts peak to peak) may be applied to pins 1 and 2. It will result in a plus or minus 50 per cent deviation from the modulator zero signal frequency (input shorted). When the anal voltage on pin 1 is positive respect to pin 2, a decrease in

modulator frequency will result and vice versa. Maximum floating voltage is 300 volts. Thus signals may be applied to pins 1 and 2 which come from "pushpull" circuits and therefore have a common voltage with respect to ground.

An internal clipping circuit limits a maximum input signal to 50 volts applied to the modulator to approximately plus or minus 4 volts.

If one side of the output of a preceding amplifier is grounded, either pin 1 or pin 2 may be connected to the ground terminal of the amplifier.

INPUT Switches-Input signals will S11, S12, S13, S14 only be recorded if the switch located above each input is at the ON position. These switches provide a convenient means of preventing accumulation without physically disconnecting the input plug. This is particularly useful when signals to the different inputs are to be recorded consecutively. Provided only on Models 400A, 400B.

S4 ADD/SUB Switch—The ADD/SUB switch determines whether incoming information is added to or subtracted from the contents of the memory. In normal use it should be in the ADD position. The SUB position may be used to subtract new information from a previously recorded response to obtain the difference between the two signals.

> TEST/USE Switch—When the TEST/ USE switch is placed in the TEST position, a test program is provided whereby one count is added to each address during each display cycle. This test checks the computer portion of the CAT to determine whether the read-write memory cycle is operating properly. The VERT. RANGE switch (S3) should be in the TEST position. When the data ADD/ SUB switch (S4) is in the ADD position the pattern displayed on the oscilloscope should uniformly move to the top of the screen and then reappear on the bottom again. The reverse happens when S4 is in the SUB position. This function is useful to move the baseline of a display on the CRT either upwards or downwards when the display appears "folded over."

**S**6

PLOT/PRINT Switch—The type of data readout may be selected with the PLOT/PRINT switch. In the PLOT position, an analog readout will be obtained. On Model CAT 400, the plotting speed of an X-Y plotter may be selected with S2 by lining up the red dot on the knob with a suitable plotting time of the outer red nomenclature. For Models CAT 400A and B see PLOT TIME control (R102) on rear panel. Plotting times are only approximate and represent the time in seconds required to plot all 400 addresses. In the PRINT position, readout will be via a digital device, such as the Model 500 Printer, the Model 530 IBM Typewriter, Models 540 or 551 Paper Tape Punch Units via the 520 Type-Punch-Read Control Unit.

S7 RESET Pushbutton—The entire memory is reset to zero by depressing the RESET button. Reset can take place only in the DISPLAY mode, thereby reducing the chance of accidental destruction of memory contents.

SL1 START Pushbutton—By depressing the START pushbutton the CAT is put into the accumulate (analysis) mode. An analysis sweep will either start at once or when an external trigger pulse is received depending on the position of S8. This mode cannot be changed by SL2, SL3, or SL4 before a full sweep is completed, i.e., any of these three pushbuttons have to be in the depressed state at the end of an analysis sweep to initiate a different mode.

SL2 DISPLAY Pushbutton—When the DIS-PLAY pushbutton is depressed, the information that has been stored in the memory is displayed on the CRT. The DISPLAY mode may be entered directly from either of the other three modes of operation.

SL3 READOUT Pushbutton—When the READOUT pushbutton is depressed, the instrument goes into a readout cycle. Readout will be either in analog or digital form depending upon the position of the PLOT/PRINT switch.

SL4 STOP Pushbutton—When the STOP pushbutton is depressed, any of the modes which have been initiated by the

other three pushbuttons (SL1, SL2, or SL3) will be terminated. All data accumulated by the CAT memory are frozen or retained by the CAT.

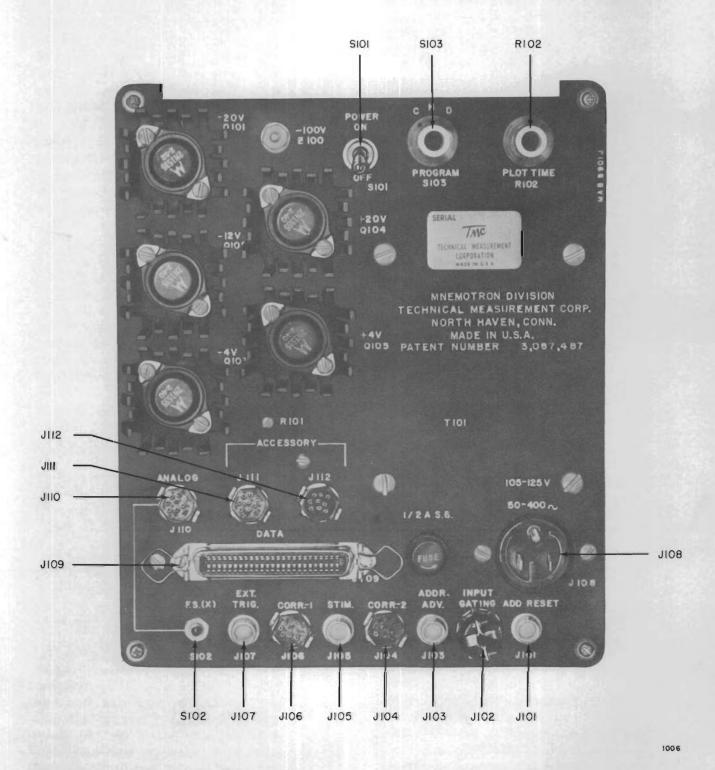

2.2.2 REAR PANEL (See figure 2-3.)

POWER ON/OFF Switch—The POWER switch applies ac power to the entire CAT. (Always turn OFF before removing covers.) The contents of the memory are not disturbed by removing the power from the CAT. When the unit is turned on again, previous contents will be displayed.

S103 PROGRAM Switch—The PROGRAM switch must be set to C for normal averaging operation or to obtain stimulus related time distributions using modulator by-pass cards. This control is not available on Model 400.

To obtain interval distributions the PROGRAM switch must be in the H position. A minimum pulse of plus 2.5 volts must be applied to connector J101 to automatically register one count in the particular address referenced at that moment, to reset the address to zero, and to start a new sweep after 50 microseconds. The pulse may be derived from external equipment.

With S103 set to D a minimum pulse of plus 2 volts applied to EXT. TRIG. (J107) will start a sweep. The sweep time is selected by the ANALYSIS TIME switch (S2). If S2 is in position EXT, the sweep time is determined by the frequency of an external pulse generator connected to the ADDR. ADV. connector (J103). A pulse applied to J101 stops the sweep, adds one count to the data contained in the address and resets the address to zero. A time of at least 50 microseconds must elapse before a new trigger pulse is applied to J107.

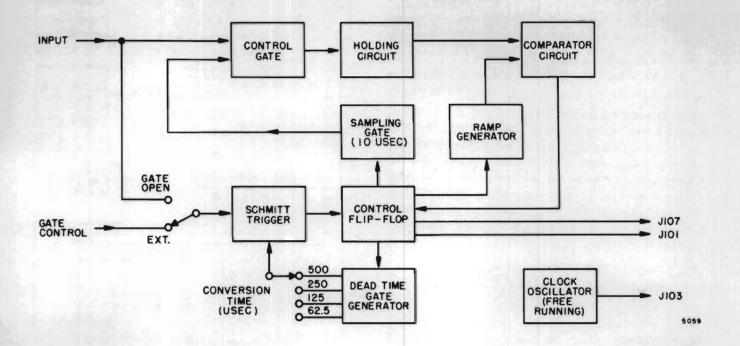

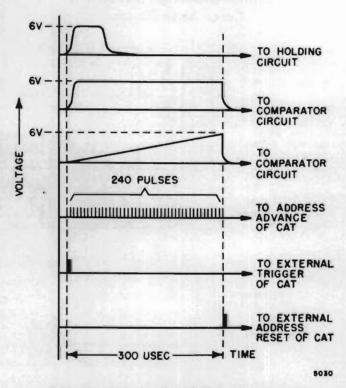

The D position is used for CAT amplitude and dwell time distributions. MNEMOTRON Model 606 Amplitude-to-Time Converter may be employed to furnish the proper signals including address advance pulses for amplitude analysis. Model 605 Amplitude Discriminator may be employed to furnish trigger and address reset pulses for dwell time analysis.

Figure 2-3. Computer of Average Transients, Model 400B, Rear View.

J107

J105

J103

J102

- R102 PLOT TIME Control—The plotting speed of an X-Y plotter can be continuously adjusted by the PLOT TIME control from approximately 12 seconds to 120 seconds for 400 addresses. Provided only with Models 400A, 400B.

- J110 ANALOG Connector—The ANALOG connector (J110) supplies analog voltages (0 to plus 100 millivolts) to operate either an X-Y Recorder or a Strip-Chart Recorder. (See table 2–5, J110, for pin connections.)

- J111 ACCESSORY Receptacles—J111 allows the CAT to be connected to an external control panel. Contacts for START, DISPLAY, READOUT, STOP and RESET functions are available. (See table 2–6, J111, for pin connections.)

J112 is provided for the connection of the Preset Sweep Counters, Models 562 and 592. (See table 2–7, J112, for pin connections.)

- J109 DATA Connector—The DATA connector (J109) provides parallel BCD information for the readout devices that can be connected to the CAT, i.e., the Model 500 Paper Tape Printer, the Model 510 Typewriter Drive Unit, or the Model 520 Type-Punch-Read Control Unit. (See table 2–4, J109, for pin connections.)

- 1/2 FUSE—Slow-blo 1/2 ampere fuse to A.S.B. protect CAT from power overload.

- Male Plug Connector—Any ac line voltage between 105 and 125 volts at a frequency between 50 and 400 cps may be used to power the CAT. Power is applied at the male plug. Transformer connections may be changed to permit operation at 210 to 230 volts, 50 to 400 cps.

- S102 F. S. (X) Pushbutton—The F. S. (X) pushbutton is used to calibrate an X-Y Recorder in the X direction. When pressed, a full scale voltage appears on the X terminal at J110 so that the recorder sensitivity can be adjusted to give full scale deflection.

- EXT. TRIG. Jack—A minimum plus 2 volt signal can be supplied to the EXT. TRIG jack (J107) to start an analysis sweep. The TRIGGER switch (S8) must be in the EXT. position. Input impedance is 6,000 ohms.

- J106 Correlator No. 1 Connector—Connects the MNEMOTRON Model COR 256 Correlator to the CAT. (For pin connections see table 2–3, J106.) Provided only on Model 400B.

- STIM. Jack—A pulse is obtained from the STIM. jack (J105) which can be used to trigger stimulation equipment either directly or through suitable external equipment. The amplitude of this pulse is plus 15 volts and the duration is approximately 10 milliseconds on Models CAT 400 and 400A. On Model CAT 400B the amplitude is plus 50 volts and the duration is approximately 10 milliseconds. The pulse will appear either at the start of an analysis sweep or at the time when the sweep enters address 20, depending on the position of the STIMULUS switch (S9).

- J104 Correlator No. 2 Connector—For connection of MNEMOTRON Model COR 256 Correlator, (See table 2–2, J104, for pin connections.)

- ADDR. ADV. Jack—The address may be advanced externally by supplying minimum plus 1 volt pulses to the ADDR. ADV. (J103) jack if analysis times other than those internally available are desired. The ANALYSIS TIME switch (S2) must be in the EXT. position. Each pulse advances the sweep by one address. The pulse frequency for a desired analysis time may be calculated from f=400/Ta where Ta is the analysis time in seconds. Input impedance is 50,000 ohms. Maximum pulse frequency is 20,000 pulses per second.

- INPUT GATING Connector—The IN-PUT GATING jack (J102) is provided for remote control of the modulator gates. To remotely enable an input gate, a ground potential must be provided to the proper pin. To turn the gate off remotely, a minus 12 volt potential must be provided to the same pin. (See table 2–1, J102, for pin connections.) This

connector also supplies an amplified X and Y analog output signal for slaving an external oscilloscope to the CAT. Provided on Model 400B only.

#### NOTE

A shorting plug, Amphenol 9-pin connector (126-220) must be inserted in J102 when the system is operated manually. It is supplied with the computer.

J101 ADDR. RESET Jack—A signal can be applied to the ADDR. RESET connector only when the PROGRAM switch (S103) is in the H or D position. A minimum pulse of plus 2.5 volts is required to operate the address reset circuitry. When the pulse is applied, the advance of the sweep will be stopped, one count will be deposited in the address just referenced and the sweep will be returned to address zero. The input impedance is 10,000 ohms. Not used on Model CAT 400.

#### 2.3 PREPARATION FOR USE AND OPERA-TION

#### 2.3.1 INTERCONNECTION PROCEDURES

Interconnection procedures for the Computer of Average Transients (CAT) are dependent upon specific applications. Section 6 outlines the uses of the CAT and their physical set-up. Tables 2–1 through 2–7 list the connections to all external equipment and are referenced in section 6. Paragraph 2.3.3 and figure 2–4 detail the mating of the CAT with the MNEMOTRON Series 600 CAT Accessories.

# 2.3.2 STARTING AND STOPPING PROCEDURE To start the Computer of Average Transients, proceed as follows:

- a. Connect CAT for particular application. Refer to the Applications Section 6 for use with ancillary equipment or paragraph 2.3.3 for use with MNEMOTRON Series 600 CAT Accessories.

- b. Connect male plug (J108) to 105-125, 50-400 cps power source. (210-230 available on request.)

- c. Position POWER switch (S101) at ON.

- d. Depress DISPLAY pushbutton (SL2).

- e. Depress RESET pushbutton (S7).

- f. Depress START pushbutton (SL1) for CAT operation.

To stop CAT, depress STOP pushbutton (SL4) until operation ceases and position POWER switch (S101) at OFF.

#### NOTE

Before initiating a new mode of operation of the CAT, always press STOP push-button first, and then the pushbutton of the desired mode. To stop accumulation (START pushbutton lighted) press the STOP pushbutton and keep it in the depressed condition at the time of completion of the analysis sweep. The button may be pressed before the end of the sweep and held; however, the sweep will always be completed due to an internal interlock. Switching from one mode directly into the other may result in loss of information in some addresses.

TABLE 2-1 J102 REMOTE INPUT CONTROL AND SCOPE OUTPUT

(Not available on Models CAT 400, 400A, and 400H)

| Pin<br>Number | Signal                    | Internal<br>Connection |

|---------------|---------------------------|------------------------|

| A             | A INPUT No. 1 control     |                        |

| В             | INPUT No. 2 control       | S12-1                  |

| C             | INPUT No. 3 control       | S13-1                  |

| D             | INPUT No. 4 control       | S14-1                  |

| E             | -12 volt supply           | PC22L-2                |

| F             | Ground                    | PC23L-4                |

| Н             | Ground                    |                        |

| J             | Y output for oscilloscope | PC11R-17               |

| K             | X output for oscilloscope | PC11R-38               |

#### NOTE

For manual control from front panel inputs switches S11 through S14, pins A, B, C, and D must be connected to ground pins F and H. A shorting plug (Amphenol 9 pin connector—126-220) is provided. For remote operation, pins A through D must be switched to minus 12 volts (pin E) individually when no signal accumulation is desired through that particular input and to ground (pins F and H) to turn on the corresponding input. Remove the shorting plug from J102 when operating in remote control mode. Pins J and K provide an amplified output of the Y and X signals for oscilloscope display.

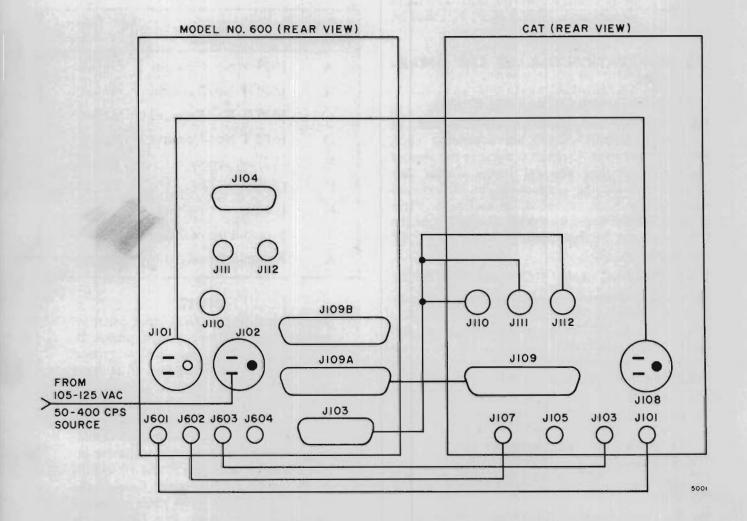

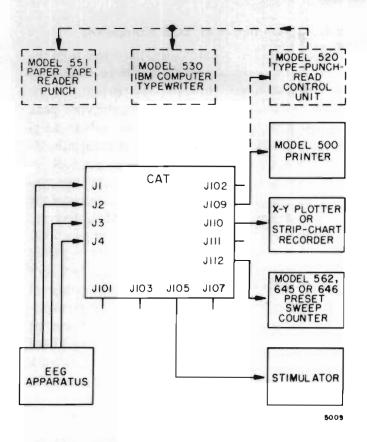

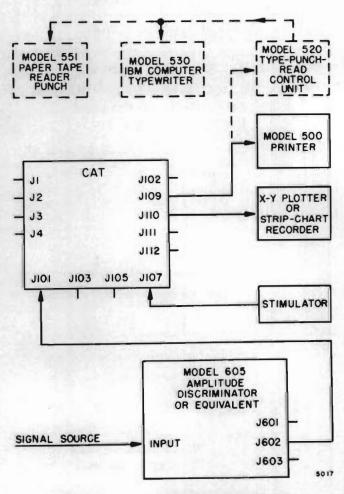

### 2.3.3 CAT INTERCONNECTIONS WITH SERIES 600 CAT ACCESSORIES (See figure 2–4.)

To connect the Series 600 Accessories to the CAT, proceed as follows:

- a. Attach BNC cable from ADDR RESET jack (J601) to CAT ADDR. RESET jack (J101). (Used only with Models 605 and 606.)

- b. Attach BNC cable from EXT TRIG jack (J601) to CAT EXT TRIG. jack (J107). (Used only with Models 605 and 606.)

- c. Attach BNC cable from EXT ADD. ADV. jack (J603) to CAT ADDR. ADV. jack (J103). (Used only with Model 606.)

- d. Position Amphenol connector at TO CAT (J103), making certain properly marked connectors at the opposite end are mounted on CAT (ANALOG J110 and ACCESSORY J111, J112) positions.

- e. Attach cable from TO CAT connector (J109A) to CAT DATA connector (J109).

- f. Attach CAT power cable from CAT male plug (J108) to 600 cabinet convenience outlet (J101).

- g. Attach Series 600 power cable from male plug (J102) to 105-125 vac, 50-400 cps power source. (210-230 available on request.)

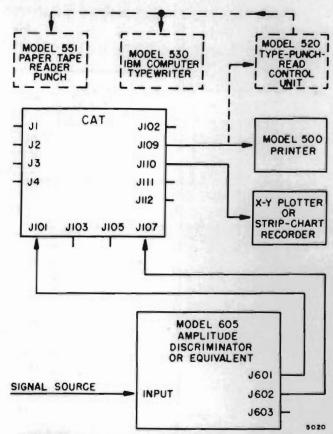

Figure 2-4. Series 600 Interconnection Diagram to CAT.

TABLE 2-2 J104 CORRELATION COMPUTER CONNECTOR (CORR-2)

(Not available on Models CAT 400, 400A, and 400H)

| Pin<br>Number | Signal            | Internal<br>Connection |

|---------------|-------------------|------------------------|

| A             | MR (memory reset) | PC5R-14                |

| В             | Not used          |                        |

| C             | Not used          |                        |

| D             | Not used          |                        |

| E             | Not used          |                        |

| F             | Not used          |                        |

| Н             | Not used          |                        |

| J             | Not used          |                        |

| K             | Not used          |                        |

#### NOTE

The MNEMOTRON Model COR 256 Correlation Computer is used in conjunction with the Model CAT 400B to form the Model CC-1 Correlation Computer System. This system provides on-line evaluation of the correlation functions.

TABLE 2-3 J106 CORRELATION COMPUTER CONNECTOR (CORR-1)

(Not available on Models CAT 400, 400A, and 400H)

| Pin<br>Number | Signal                       | Internal<br>Connection |

|---------------|------------------------------|------------------------|

| A             | ADA 1 (Address Advance)      | PC3R-12                |

| В             | AFF- (Accumulate Flip-Flop)  | PC1R-17                |

| C             | ACPB (Accumulate Pushbutton) | PC1R-8                 |

| D             | STPB (Start Pushbutton)      | PC13R-20               |

| E             | SOC (Start of Conversion)    | PC12L-19               |

| F             | ADD BUS                      | PC14R-33               |

| н             | SUB BUS                      | PC14R-31               |

| J             | IA1 (Inhibit Accumulate)     | PC2R-26                |

| K             | RZ (Reset Zero)              | PC23R-39               |

TABLE 2-4 J109 DATA CONNECTOR

| Pin<br>Numbe | er Sigr    | nal                  | Internal<br>Connection |

|--------------|------------|----------------------|------------------------|

| 1            | 1          |                      | PC26R-54               |

| 2            | 2          | - 100                | <b>-5</b> 5            |

| 3            | 4          | Data 10°             | -56                    |

| 4            | 8          |                      | -57                    |

| 5            | 1          |                      | -58                    |

| 6            | 2          | Data 101             | -59                    |

| 7            | 4          | Data 10 <sup>1</sup> | -60                    |

| 8            | 8          |                      | -61                    |

| 9            | 1          |                      | -62                    |

| 10           | 2          | Data 10 <sup>2</sup> | -63                    |

| 11           | 4          | Data 10              | -64                    |

| 12           | 8          |                      | Arith-<br>metic -65    |

| 13           | 1          | Data 10³             | Scaler –66             |

| 14           | 2          |                      | -67                    |

| 15           | 4          | Butu 10              | -68                    |

| 16           | 8          |                      | -69                    |

| 17           | 1 ]        |                      | -70                    |

| 18           | 2          | Data 10 <sup>4</sup> | -71                    |

| 19           | 4          | Duta 10              | -72                    |

| 20           | 8          |                      | -73                    |

| 21           | 1          |                      | -74                    |

| 22           | 2          | Data 10 <sup>5</sup> | -75                    |

| 23           | 4          | Data 10              | -76                    |

| 24           | 8          |                      | -77                    |

| 25           | -100 volts |                      | -78                    |

| 26           | 1          | l die                | -79                    |

| 27           | 2          | Arith-<br>metic      | -80                    |

| 28           | 4          | Shift                | -81                    |

| 29           | 8          |                      | -82                    |

| 30           | Read Trigg | ger (no filte        | r) PC2R-28             |

| 31           |            |                      | PC26R-84               |

| 32           |            |                      | -85                    |

| 33           |            |                      | -86                    |

TABLE 2-4 J109 DATA CONNECTOR (CONT'D)

| Pin<br>Numbe | r Signal        |           | Inte<br>Conne |      |

|--------------|-----------------|-----------|---------------|------|

| 34           | 1 ]             |           | PC26F         | R-87 |

| 35           | _               | ddress    |               | -88  |

| 36           | 4 10            | ecade     |               | -89  |

| 37           | 8               |           |               | -90  |

| 38           | 1 )             | ELM       | Address       | -91  |

| 39           |                 | ddress    | Register      | -92  |

| 40           | 4 D             | ecade     |               | -93  |

| 41           | 8               | 11:50     |               | -94  |

| 42           | 1 ) 6           | -16 4     |               | -95  |

| 43           | 2 } 80          | cale of 4 | Street, St.   | -96  |

| 44           |                 |           |               | -97  |

| 45           |                 |           |               | -98  |

| 46           | Print Trigger   |           |               | -99  |

| 47           | Address Advar   | nce       | PC:           | 5R-9 |

| 48           | Shift Trigger   |           | PC13I         | R-16 |

| 49           | Write-in Trigge | er        | PC2I          | R-25 |

| 50           | Chassis Ground  | d         | PC26          | -108 |

TABLE 2-5 J110 ANALOG CONNECTOR

| Pin<br>Number | Signal                                                                                                       | Internal<br>Connection |

|---------------|--------------------------------------------------------------------------------------------------------------|------------------------|

| A             | Recorder ground X terminal (RXG)                                                                             | PC11R-30               |

| В             | Recorder X signal (RX+) + 100 mv.                                                                            | PC11R-31               |

| С             | Recorder ground Y terminal (RYG)                                                                             | PC11R-14               |

| D             | Recorder Y signal (RY+) + 100 mv.                                                                            | PC11R-13               |

| E             | Ground. This is to be connected to the frame of the X-Y plotter. X and Y servo amplifier should be floating. | PC26-110               |

| F             | NDR (Null Detector Rush)                                                                                     | PC26R-106              |

| Н             | RFF+ (high level) (Readout flip-flop)                                                                        | PC26R-104              |

| J             | -26 volts (unregulated)                                                                                      | PC20L-8                |

| K             | Not used                                                                                                     |                        |

TABLE 2-6 J111 REMOTE CONTROL ACCESSORY CONNECTOR

| Pin<br>Number | Signal                                      | Internal<br>Connection |

|---------------|---------------------------------------------|------------------------|

| A             | External STOP control (switch to ground)    | PC1R-18                |

| В             | External READOUT control (switch to ground) | PC1R-30                |