GA34-0033-3

File No. S1-01

IBM Series/1

User's Attachment

Manual

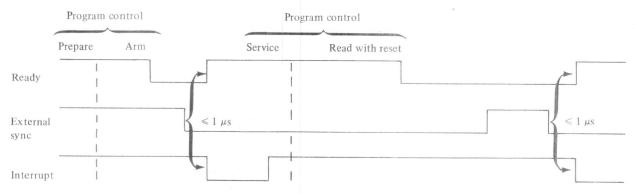

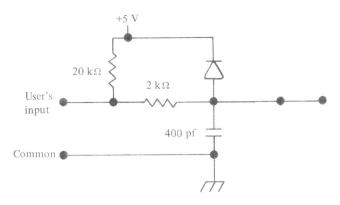

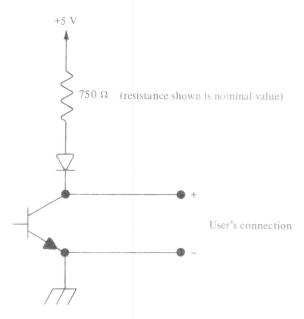

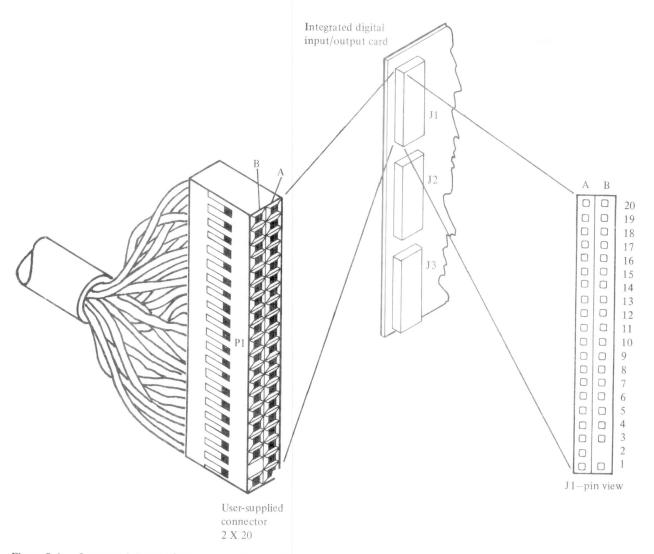

#### Fourth Edition (September 1979)

This is a major revision of, and obsoletes, GA34-033-2 and Technical Newsletter GN34-0448. This revision includes editorial and technical changes, which incorporate information about the IBM 4952 Processor and the IBM General Purpose Interface Bus (GPIB) Adapter. Because of the extensive changes, revision bars have been omitted; this manual should be reviewed in its entirety.

Use this publication only for the purpose stated in the Preface.

Changes are periodically made to the information herein; any such changes will be reported in subsequent revisions or Technical Newsletters.

It is possible that this material may contain reference to, or information about, IBM products (machines and programs), programming, or services which are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Publications are not stocked at the address given below. Requests for copies of IBM publications should be made to your IBM representative or the IBM branch office serving your locality.

This publication could contain technical inaccuracies or typographical errors. A form for readers' comments is provided at the back of this publication. If the form has been removed, address your comments to IBM Corporation, Systems Publications, Department 27T, P.O. Box 1328, Boca Raton, Florida 33432. IBM may use and distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

This publication provides reference information to aid in designing logic for communicating with an IBM Series/1 processor through the input/output channel and several designated user attachment features. This information is intended primarily for experienced engineers or technicians. This publication is also useful to customers who need detailed information for connecting their instruments and devices to the various attachment features.

The reader should have a working knowledge of the information in the appropriate IBM Series/1 processor and processor features description manual.

The processor I/O channel architecture, or any aspect of the I/O interfaces described in this publication, may be altered from time to time by IBM or may be withdrawn by IBM in part or in whole.

This manual is organized as follows:

Chapter 1. Introduction describes the I/O channel and the user attachment features.

Chapter 2. Processor I/O Channel describes the channel direct program control (DPC) operations, cycle-steal (CS) operations, interrupts, and initial program load (IPL).

Chapter 3. Timer Feature describes the timer feature, including signal lines, interrupts, electrical characteristics, and physical characteristics.

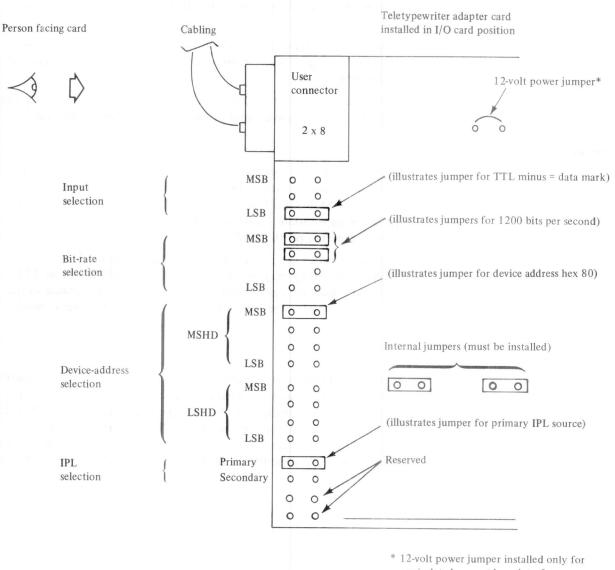

Chapter 4. Teletypewriter Adapter Feature describes the teletypewriter adapter feature, including interface options, timing sequences, electrical characteristics, and physical characteristics.

Chapter 5. Integrated Digital Input/Output Feature describes the integrated digital input/output feature, including operational, electrical, and physical characteristics.

Chapter 6. Customer Direct Program Control (DPC) Adapter Feature describes the customer direct program control adapter feature, including operational, electrical, and physical characteristics.

Appendix A. General Purpose Interface Bus Adapter, RPQ D02118, describes the Series/1 implementation of the digital interface contained in IEEE Standard 488, including the commands and functions used by the General Purpose Interface Bus (GPIB) Adapter.

*Note:* Installation instructions are shipped with each system order. These instructions contain the information required for selecting options and device addresses on the I/O attachment feature cards.

## **Related Publications**

Additional publications are listed in the *IBM Series/1 Graphic Bibliography*, GA34-0055.

# **Contents**

| Chapter 1. Introduction 1-1                                                                   | Pulse Duration Counter 3-8                                                     |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Processor I/O Channel 1-2                                                                     | Timer Feature Operational Characteristics 3-8                                  |

| Channel Repower Feature 1-2                                                                   | Interrupts 3-8                                                                 |

| Channel Socket Adapter Feature 1-2                                                            | Interrupt Presentation 3-9                                                     |

| I/O Attachment Features 1-2                                                                   | Status After Power Transitions and Resets 3-9                                  |

| Timer Feature 1-2                                                                             | Timer Feature Electrical Characteristics 3-10                                  |

| Teletypewriter Adapter Feature 1-3                                                            | Timer Feature Physical Characteristics 3-11                                    |

| Integrated Digital Input/Output (I/O) Nonisolated                                             | Signal Pin Assignments 3-11                                                    |

| Feature 1-3                                                                                   | Pin Assignments Showing Customer Access Panel (CAP)                            |

| Customer Direct Program Control (DPC) Adapter                                                 | Connections 3-12                                                               |

| Feature 1-3                                                                                   | Jumper Selections 3-12                                                         |

| Customer Access Panel (CAP) Feature 1-3                                                       | Timer Feature Design Considerations 3-12                                       |

| General Purpose Interface Bus Adapter Feature 1-3                                             | Wiring Practices 3-12                                                          |

| 1                                                                                             | Application Notes 3-12                                                         |

| Chapter 2. Processor I/O Channel 2-1                                                          |                                                                                |

| Introduction 2-1                                                                              | Chapter 4. Teletypewriter Adapter Feature 4-1                                  |

| Functional Description of I/O Channel Signal Lines 2-2                                        | Introduction 4-1                                                               |

| Signal Line Groups 2-3                                                                        | Relationship to Other Features 4-4                                             |

| Functional Subsets of the Signal Lines 2-4                                                    | Application Summary 4-4                                                        |

| Service Group Line Definitions 2-7                                                            | Data Transmission 4-11                                                         |

| Poll Group Line Definitions 2-12                                                              | Initial Program Load 4-12                                                      |

| Processor I/O Channel Operational Characteristics 2-15                                        |                                                                                |

| Operational Sequences on the Channel 2-15                                                     | Teletypewriter Adapter Operational Characteristics 4-12                        |

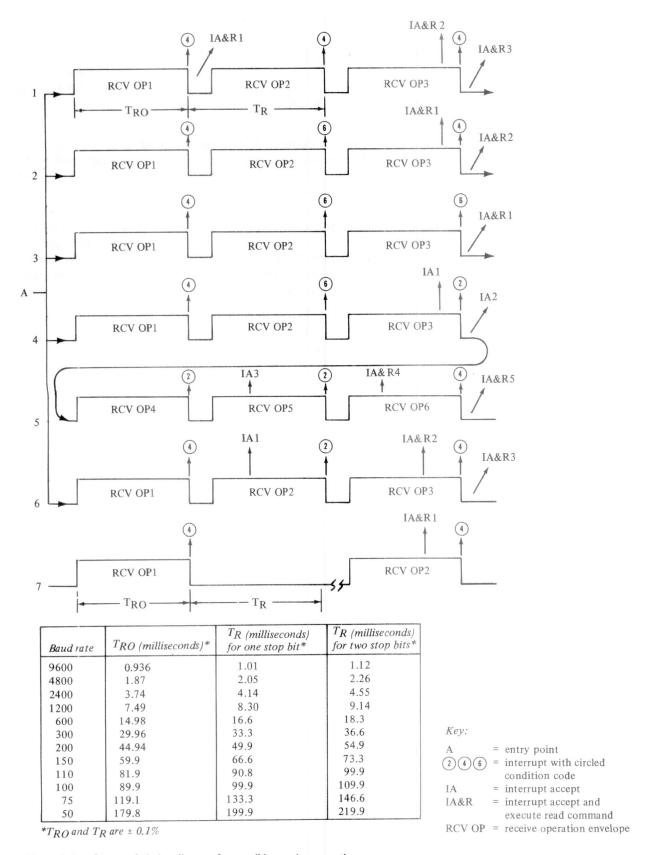

| DPC Sequence Description 2-19                                                                 | Types of Receive Operations 4-13                                               |

| Interrupt-Service Sequence Description 2-22                                                   | Interrupt Presentation 4-14                                                    |

| Cycle-Steal Service Sequence Description 2-24                                                 | Commands That Initiate Receive and Transmit                                    |

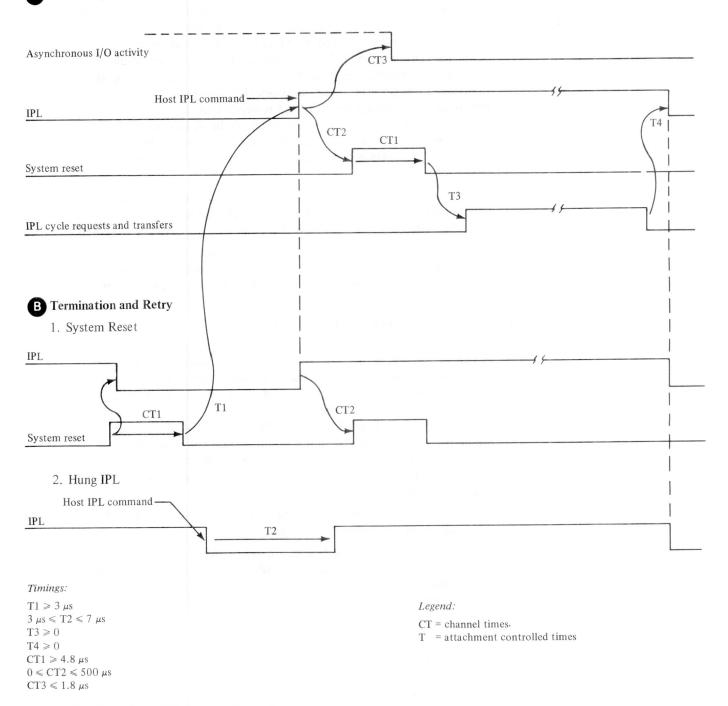

| Poll Sequence Description 2-27                                                                | Operations 4-15                                                                |

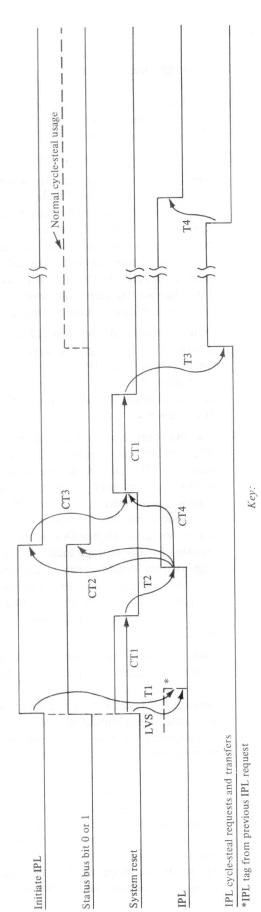

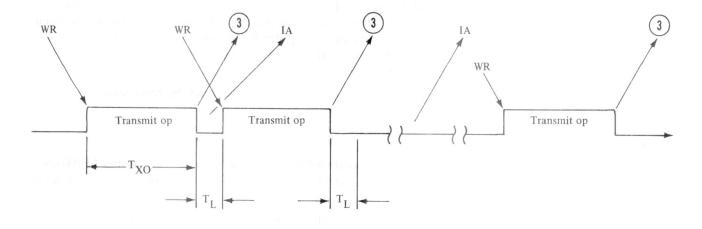

| Processor-Initiated IPL Sequence Description 2-33                                             | Transmit Operations 4-16                                                       |

| Host-Initiated IPL Sequence Description 2-36                                                  | Receive Operations 4-17                                                        |

| Reset Sequences Description 2-39                                                              | Read Control and Write Control 4-20                                            |

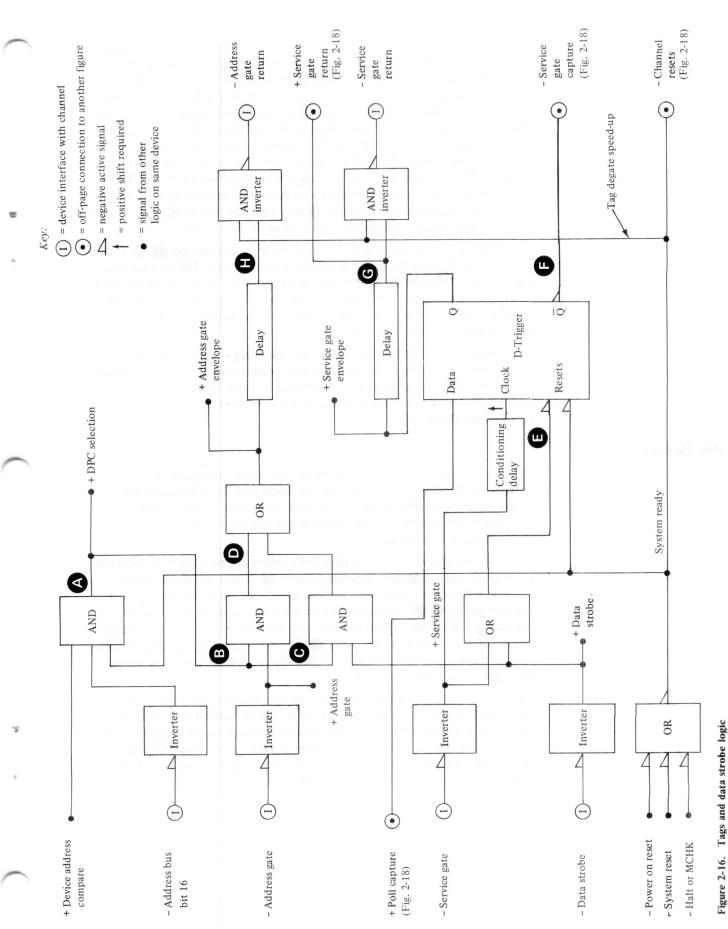

| Design Considerations for Operational Sequences 2-39                                          | System-Related Characteristics 4-21                                            |

| Operational Power Considerations 2-48                                                         | Teletypewriter Adapter Electrical Characteristics 4-22                         |

| Processor I/O Channel Electrical Characteristics 2-50                                         | Teletypewriter Adapter Communications Lines 4-22                               |

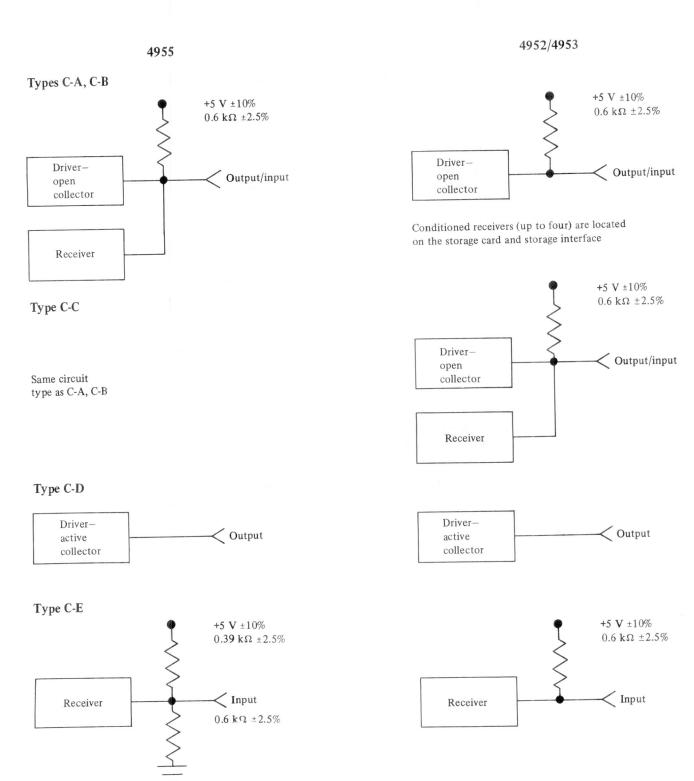

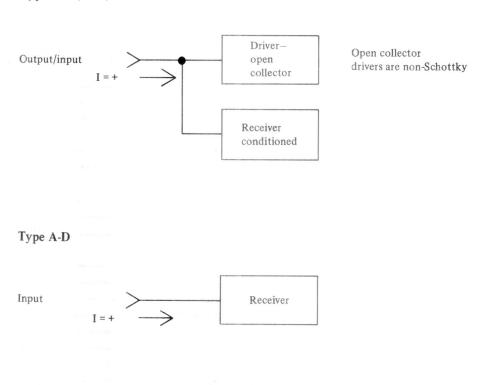

| Channel Signal Line Electrical Characteristics 2-50                                           | Driver/Receiver Information 4-26                                               |

| Driver/Receiver Information 2-53                                                              | Power Supplies 4-28                                                            |

| Other Attachment Considerations 2-65                                                          | Teletypewriter Adapter Physical Characteristics 4-29                           |

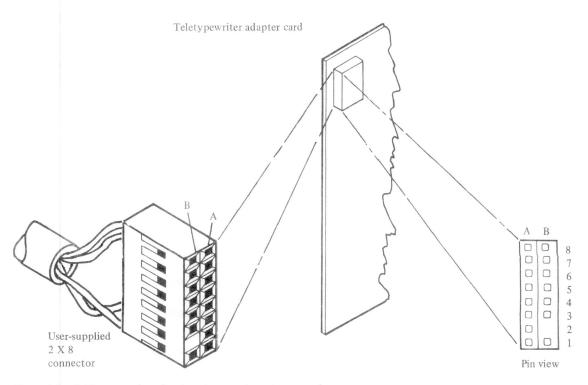

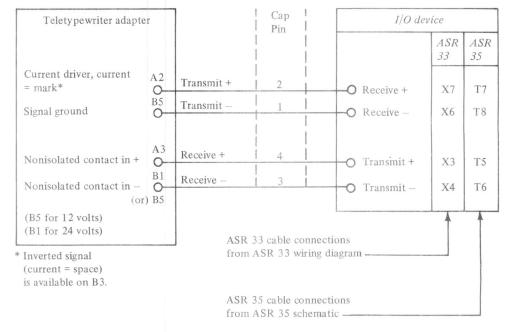

|                                                                                               | Physical Description 4-29                                                      |

| Power Supply Electrical Characteristics 2-66                                                  | Signal Pin Assignments 4-29                                                    |

| Processor I/O Channel Physical Characteristics 2-66                                           | Teletypewriter Adapter Design Considerations 4-30                              |

| Signal Pin and Cable Assignments 2-66                                                         | Teletypewriter Device Information 4-30                                         |

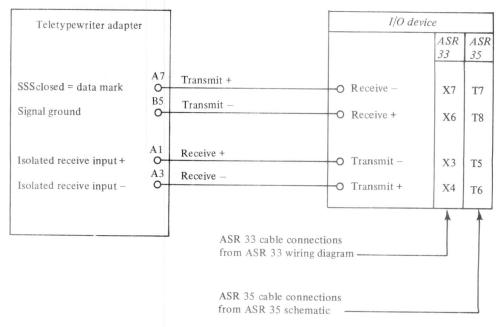

| I/O Channel Physical Components Description 2-70 Sequence of Plugging Device Attachments 2-73 | Cable Connection to the Teletypewriter Adapter 4-30                            |

|                                                                                               | Customer Access Panel (CAP) Connections 4-33                                   |

| Processor I/O Channel Attachment Features 2-73 Channel Repower Feature 2-73                   |                                                                                |

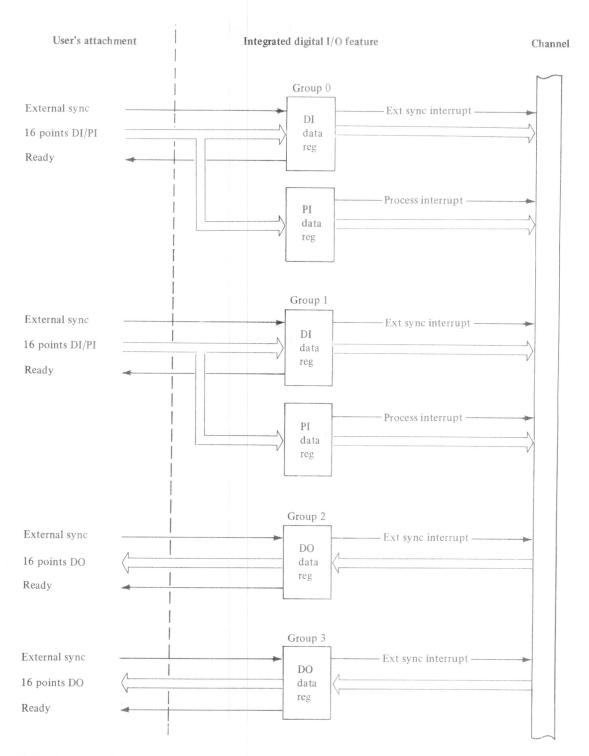

|                                                                                               | Chapter 5. Integrated Digital Input/Output Feature 5-1                         |

| Socket Adapter Feature 2-77                                                                   | Introduction 5-1                                                               |

| Chapter 3. Timer Feature 3-1                                                                  | Digital Input (DI) 5-1                                                         |

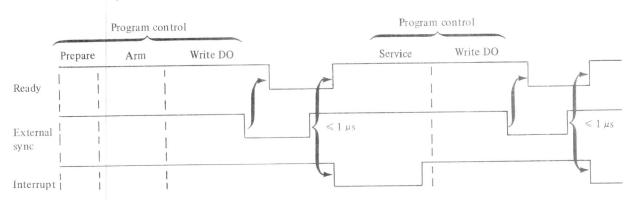

| Introduction 3-1                                                                              | Digital Output (DO) 5-4                                                        |

| Relationship to Other Features 3-3                                                            | Integrated Digital I/O Operational Characteristics 5-4                         |

| Application Summary 3-3                                                                       | Digital Output Operation 5-4                                                   |

| Functional Description of the External Timer Signal                                           | Digital Input Operation 5-6                                                    |

| Lines 3-6                                                                                     | Integrated Digital I/O Electrical Characteristics 5-7                          |

| Signal Line Considerations 3-7                                                                | Digital Input (DI) Characteristics 5-7                                         |

| Application Sequences 3-7                                                                     | Digital and 'External Sync' Input Specifications 5-7                           |

| Interval Timer 3-7                                                                            | Digital Output (DO) Characteristics 5-8                                        |

| Pulse Counter 3-8                                                                             | Digital and 'Ready' Output Specifications 5-9                                  |

| * WALL COMMENT OF                                                                             | Integrated Digital I/O Physical Characteristics 5-9 Signal Pin Assignments 5-9 |

|                                                                                               | Signal rin Assignments 5-9                                                     |

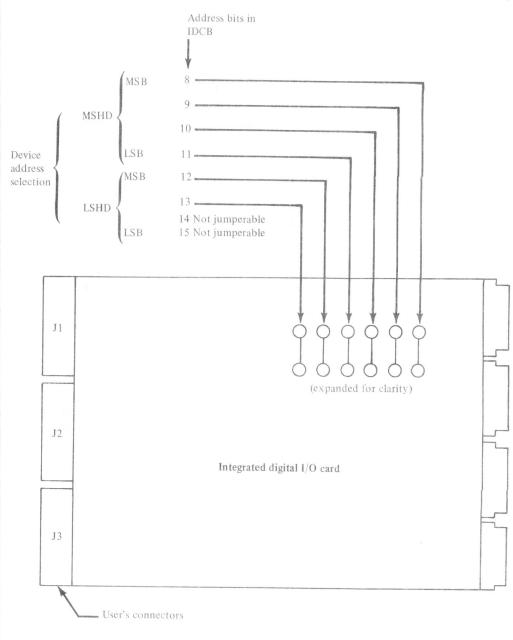

Integrated Digital I/O to Customer Access Panel Connections 5-12 Jumper Selections 5-17 Integrated Digital I/O Design Considerations 5-18 Application Notes 5-18

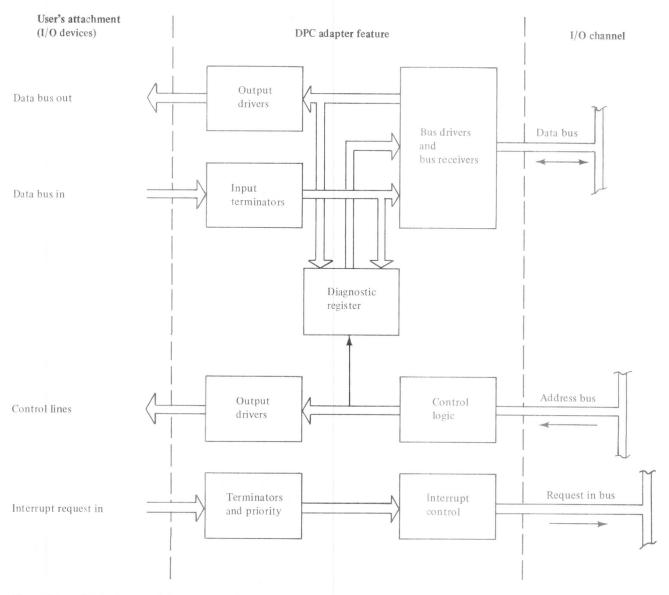

## Chapter 6. Customer Direct Program Control (DPC) Adapter

Feature 6-1

Introduction 6-1

Relationship to Other Features 6-1

Application Summary 6-2

Functional Description of the DPC Adapter Signal Lines 6-3

I/O Active 6-3

Function Bits 6-4

Modifier Bits 6-4

Device Address 6-4

Data Bus Out 6-5

Interrupt Service Active 6-5

Strobe 6-5

Data Bus In 6-6

Interrupt Request 6-6

Condition Code In 6-6

Select Response 6-6

Halt or MCHK 6-7

System Reset 6-7

Power-On Reset 6-7

Diagnostic Mode and Diagnostic Mode Modifier 6-7

DPC Adapter Operational Characteristics 6-8

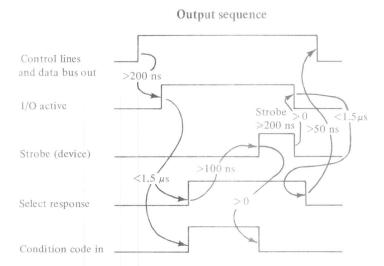

Output Sequence 6-8

Input Sequence 6-9

Interrupt-Service Sequence 6-10

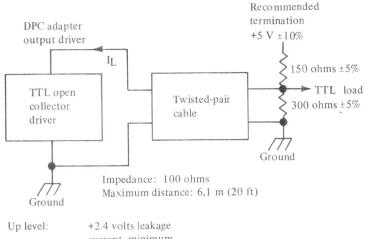

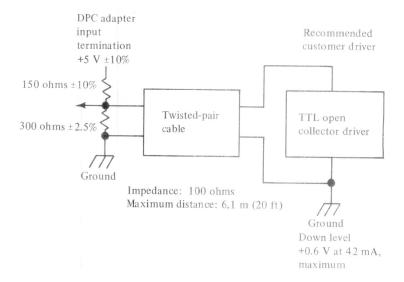

DPC Adapter Electrical Characteristics 6-11

Drivers 6-11

Receivers 6-12

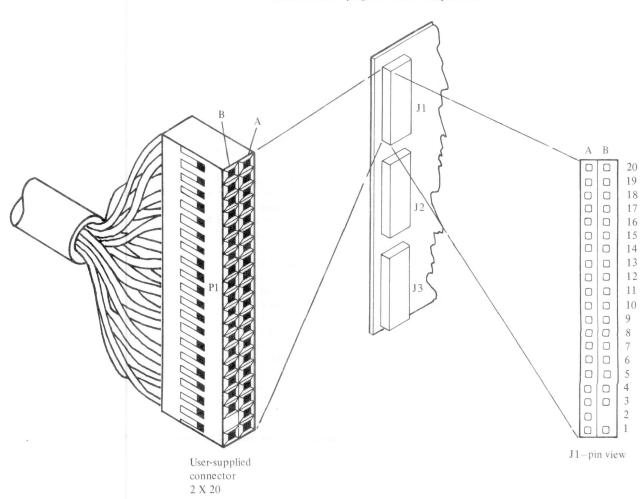

DPC Adapter Physical Characteristics 6-13

Signal Pin Assignments 6-13

DPC Adapter to Customer Access Panel Connections 6-17

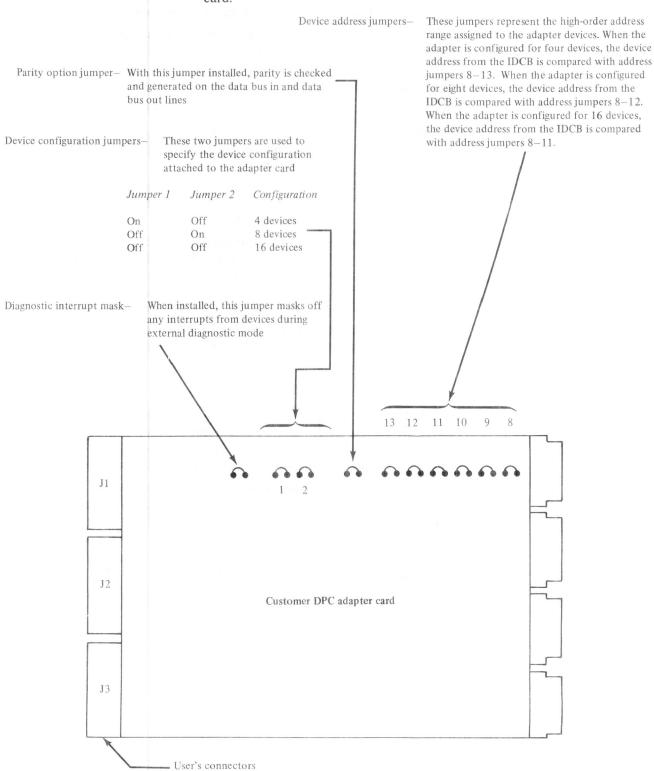

Jumper Selections 6-21

DPC Adapter Design Considerations 6-22

Application Notes 6-22

## Appendix A. General Purpose Interface Bus Adapter (RPQ D02118) A-1

Introduction A-1

Adapter Functional Description A-1

Adapter Hardware Description A-2

Adapter Command Functions A-2

Application Summary A-5

Implementation of IEEE Standard 488 A-5

Index X-1

# Chapter 1. Introduction

A variety of interfaces are provided for attachment of the user's own input/output (I/O) devices and instruments to an IBM Series/1 processor. Serial and parallel data paths, and a multifunction timer are provided. The user may choose one of the I/O adapter features or design an I/O adapter to communicate directly with the processor I/O channel.

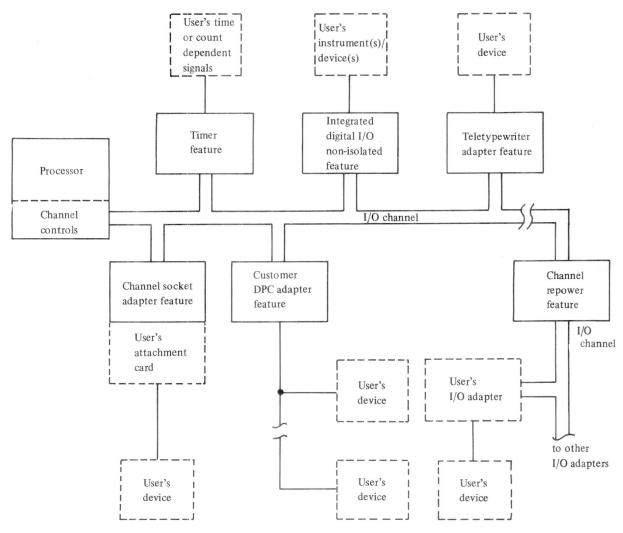

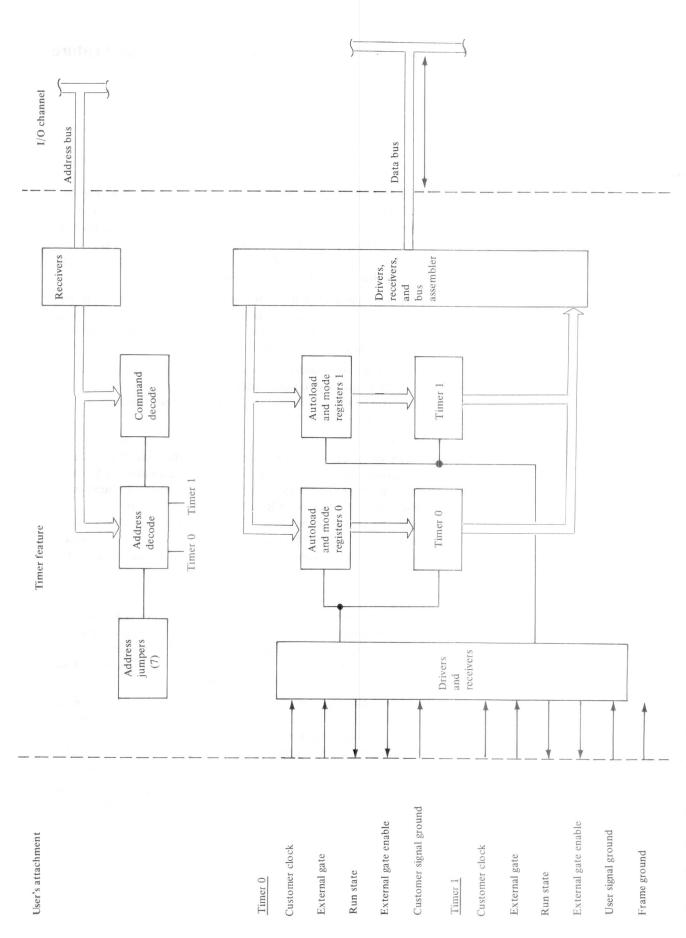

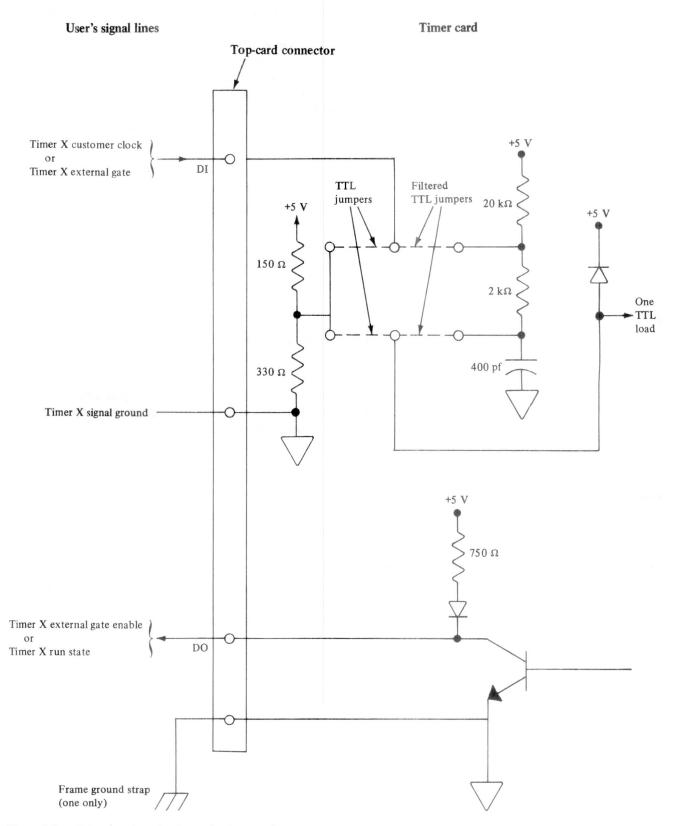

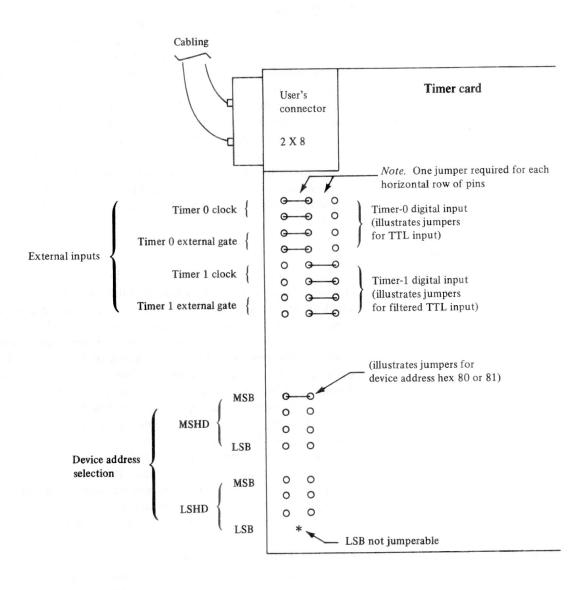

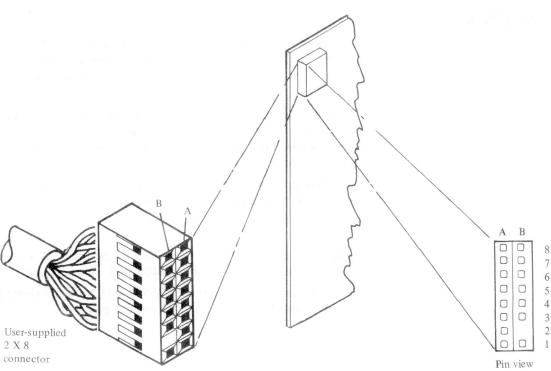

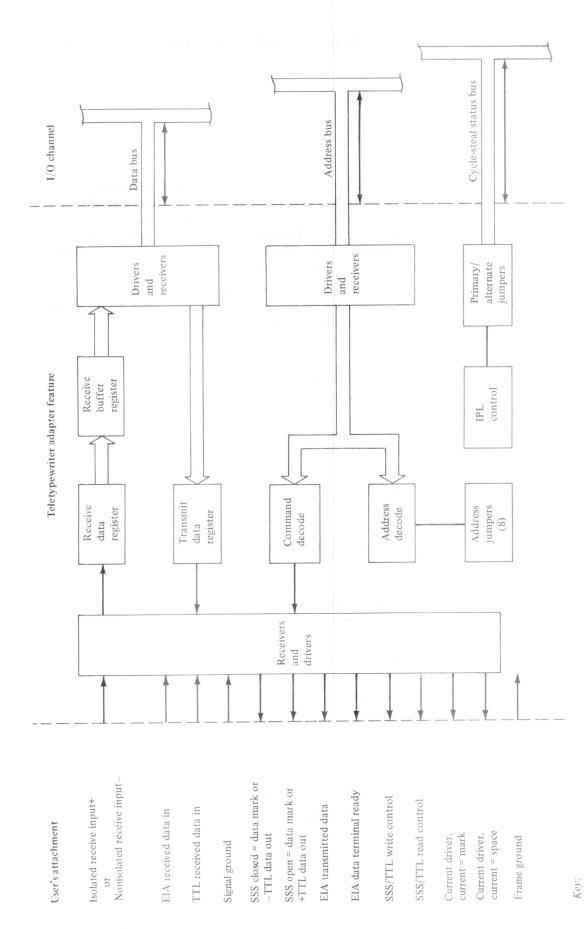

Figure 1-1 shows the various methods of attachment and the available attachment features. Each attachment is described in subsequent sections of this chapter.

Figure 1-1. Relationship of user attachments to the processor I/O channel

# Processor I/O Channel

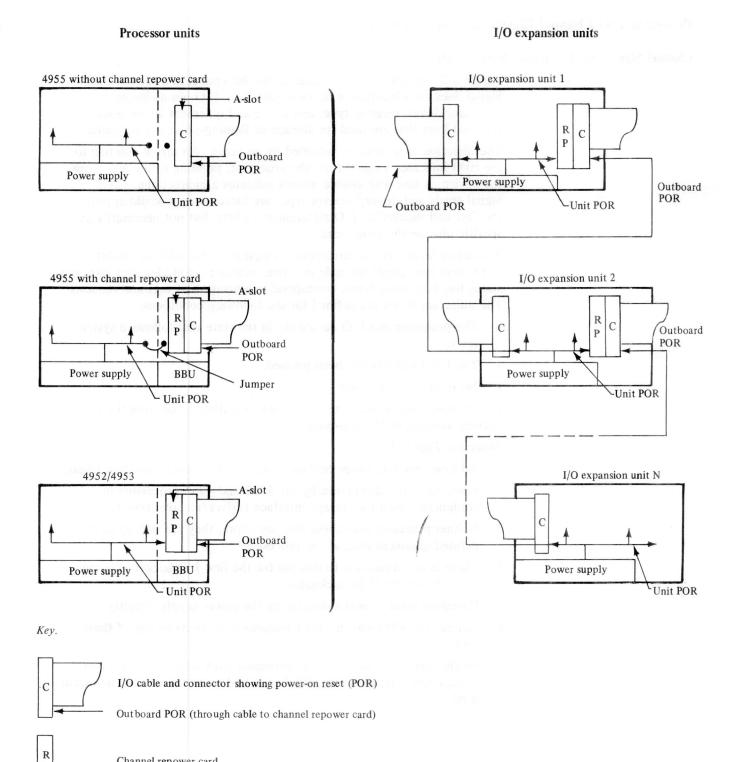

Input/output devices are attached to the processor through the I/O channel. The channel, which can accommodate 256 device addresses, (1) directs the flow of information between the I/O devices and main storage and (2) contains the facilities for the control of the I/O operations. The channel is asynchronous, with multidropped lines that link the processor resource to its external facilities. I/O channel architecture includes address, control, and data signal lines.

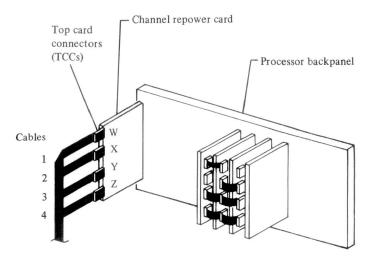

## **Channel Repower Feature**

The channel repower feature isolates and redrives the I/O channel signal and tag lines. The feature is used to extend the channel beyond the processor enclosure.

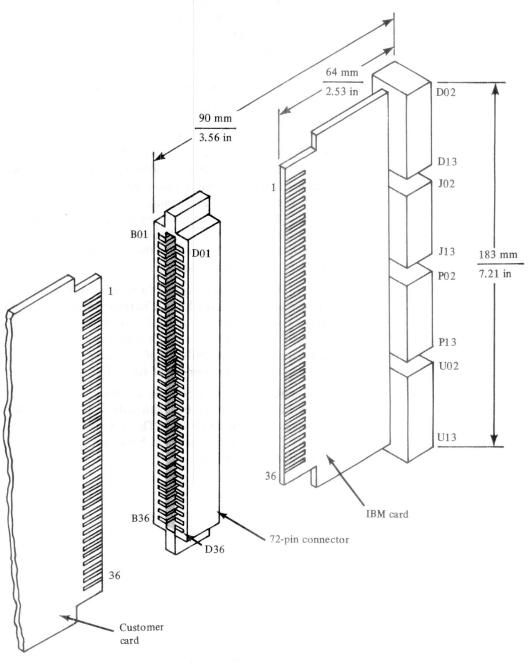

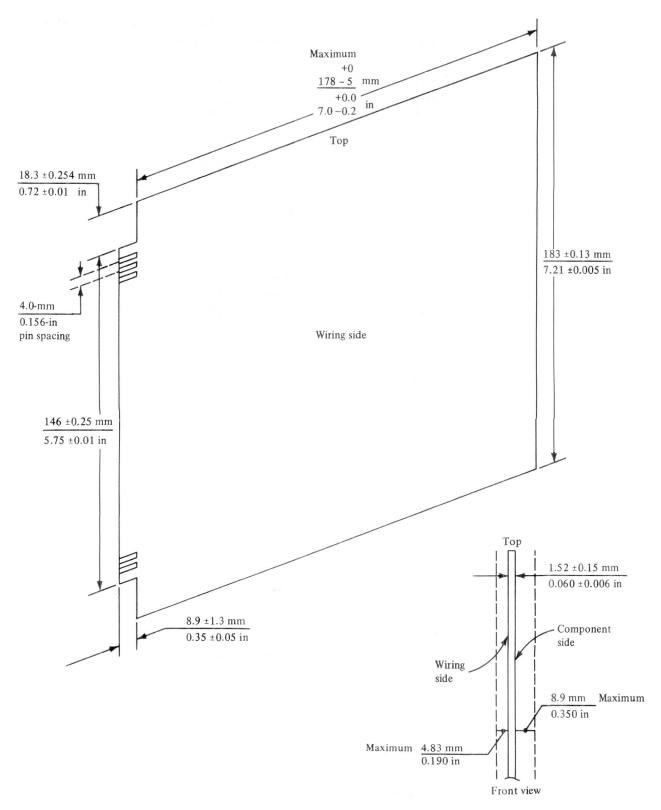

## **Channel Socket Adapter Feature**

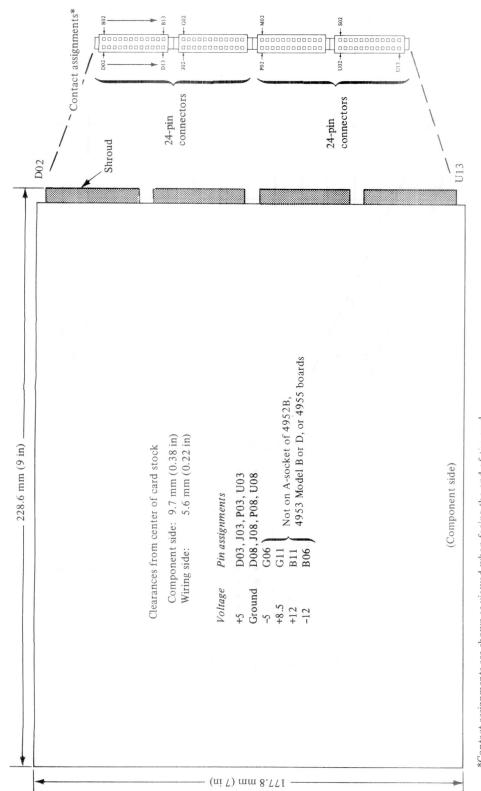

The channel socket adapter feature consists of an IBM printed circuit card that plugs into the backpanel of an IBM Series/1 processor or the IBM 4959 I/O Expansion Unit. The top edge of the IBM printed circuit card has an industry-standard connector that accepts the user's I/O adapter card. To power the user's circuits, +5 volts dc at 3 amperes, maximum, is available at the connector.

## I/O Attachment Features

The following I/O attachment features are available:

- · Timer feature

- Teletypewriter adapter feature

- Integrated digital I/O nonisolated feature

- Customer direct program control (DPC) adapter feature

#### **Timer Feature**

The timer feature card has two separately addressable 16-bit timers. If desired, time base and gating signals can be supplied, by the user, through a connector on the top of the card.

Each timer can generate periodic or aperiodic interrupts with or without the external gate.

Each timer can operate as an interval timer or pulse counter, or it can operate as a self-contained pulse duration counter with end interrupt.

# Teletypewriter Adapter Feature

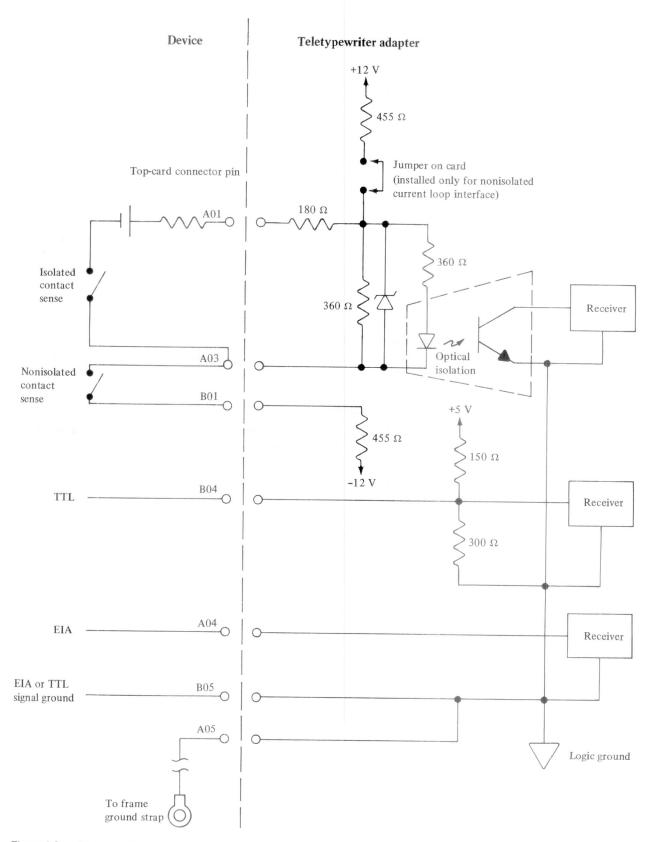

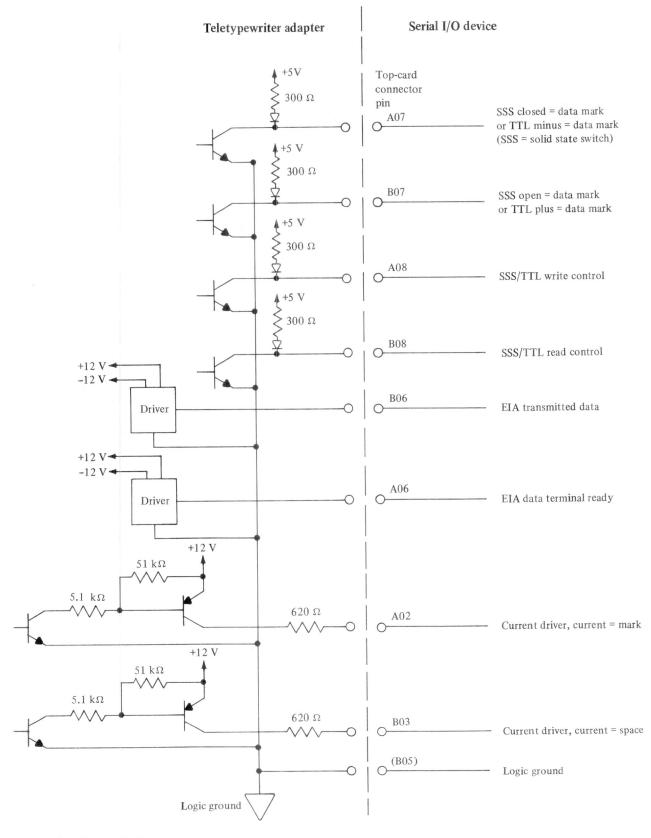

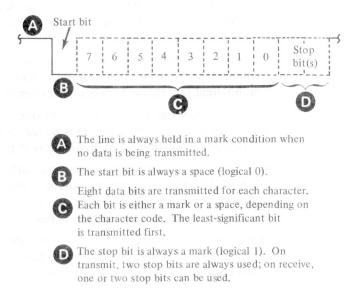

The teletypewriter adapter feature card provides a way of attaching a serial I/O device. This feature provides a logical subset of the Electronic Industries Association (EIA) RS232-C interface. Full-duplex operation and initial program load (IPL) are supported by the adapter.

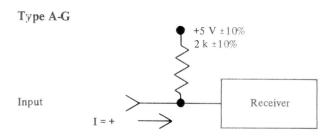

Attachment to a teletypewriter is by a dc-current loop (isolated or nonisolated). Two other attachment options are offered: a TTL-compatible interface and an EIA voltage-level interface.

# Integrated Digital Input/Output (I/O) Nonisolated Feature

The integrated digital I/O nonisolated feature card contains:

- Two 16-point groups of nonisolated digital input/process interrupt (DI/PI)

- Two 16-point groups of nonisolated digital output (DO)

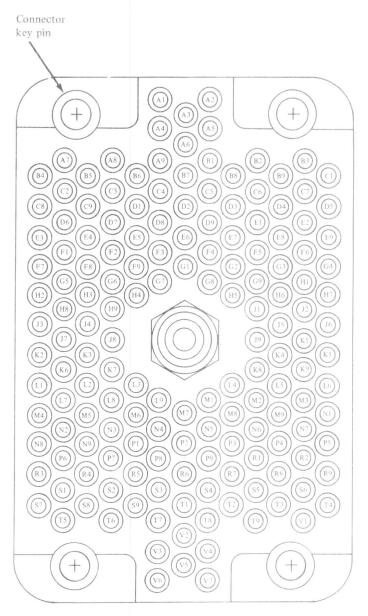

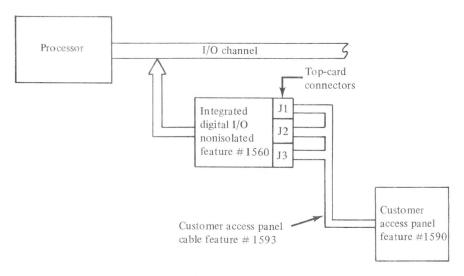

Each group of DI/PI and DO has a 'ready' and a 'sync' line for synchronizing operations with attached devices. The digital points for each group and their associated 'ready' and 'sync' lines are available at three top-card connectors.

## Customer Direct Program Control (DPC) Adapter Feature

The direct program control (DPC) adapter feature card supplies a logical subset of the I/O channel architecture. This feature provides a convenient means of attaching I/O devices and subsystems to an IBM Series/1 processor, The interface circuits are TTL compatible. The adapter is designed to perform direct program control functions only. The feature card can be configured to accommodate 4, 8, or 16 I/O device addresses. The adapter allows for interrupt vectoring of 16 interrupt sources.

There are 75 signal lines. These include: 18 data bus out, 18 data bus in, 16 interrupt request in, three function bits, four modifier bits, four device address bits, and 12 control and response lines. The data flow is always 16 bits without parity option or 18 bits with parity option (two parity bits). User attachment is through three top-card connectors.

# Customer Access Panel (CAP) Feature

The customer access panel (CAP) feature provides an assembly for mounting optional, quick-disconnect-type connectors for I/O equipment. The assembly can accommodate one timer connector, one teletypewriter connector, and up to four connectors for either the integrated digital I/O feature or the customer direct program control (DPC) feature.

The assembly mounts to the standard EIA RS310B rack-mounting screw holes at the rear of the enclosure frame.

# General Purpose Interface Bus Adapter Feature

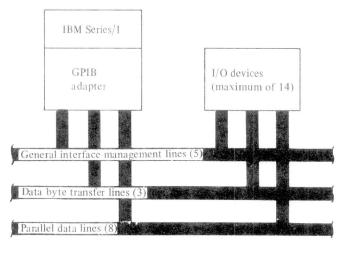

The IBM Series/1 General Purpose Interface Bus (GPIB) Adapter, RPO D02118, provides a 65K-byte cycle-steal interface for attaching up to 14 digital I/O devices to an IBM Series/1 processor. The devices attached via the GPIB adapter must conform to the requirements described in IEEE Standard 488-1978.

# Chapter 2. Processor I/O Channel

### Introduction

Input/output devices communicate with the processor and main storage devices through the processor I/O channel. Attachment of the devices to the channel is through an I/O adapter or I/O attachment logic card.

The channel directs the flow of information between the I/O devices, the processor, and main storage. A maximum of 256 devices can be logically addressed.

The processor I/O channel supports the following basic types of operations:

- Direct program control (DPC) operations—an immediate data transfer is made between main storage and the device for each Operate I/O instruction. The data may consist of one byte or one word. The operation may or may not terminate with an interrupt.

- Cycle-steal operations—an Operate I/O instruction can initiate cycle-stealing data transfers of up to 65,535 bytes (per device control block) between main storage and the device. Cycle-steal operations are overlapped with processing operations. Word or byte transfers, device control block (DCB) chaining, burst mode, and program-controlled interrupts can be supported.

- Interrupt servicing operations—four preemptive priority interrupt levels are available to facilitate device service. The device-interrupt level is assignable by the program, and the device-interrupt capability can be masked under program control.

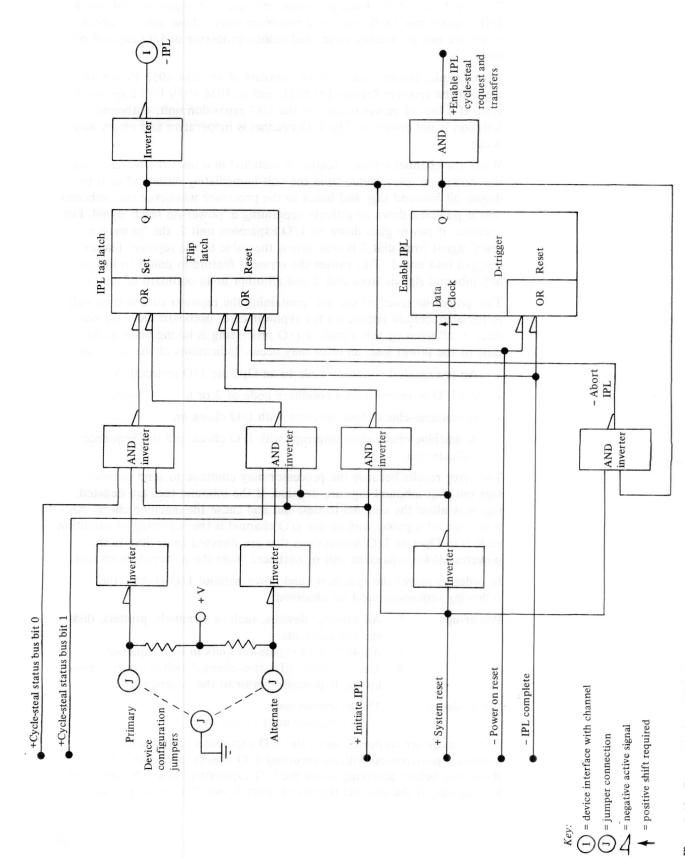

- Initial program load (IPL) operations—a record consisting of initial instructions for the processor is read into storage from either a local I/O device or from a host system.

The channel provides comprehensive error checking, including time-outs, sequence checking, and parity checking. Reporting of errors, exceptions, and status is accomplished by (1) recording condition codes in the processor during execution of Operate I/O instructions, and (2) recording condition codes and an interrupt information byte (IIB) in the processor during interrupt acceptance. Additional status words may be used by the device, as necessary, to describe its status.

The I/O channel is asynchronous and multidropped. Asynchronous means that there are no timing restrictions inherent in the architecture. The response from a given I/O device triggers the next sequential action rather than a specified timing condition. (Time-out conditions for error detection are not excluded.) An asynchronous channel allows the attachment of devices that have various speeds and technologies over a wide range of distances or delays.

All I/O channel signal lines are TTL-level compatible. This allows the user freedom in the design of I/O channel attachments.

The I/O channel signal lines are distributed internally via the processor backpanel board to each I/O attachment card socket. Distribution of the channel signal lines can be continued by connecting cables or a channel repower feature from a processor I/O socket (usually the A-socket) to an adjacent I/O expansion unit, as the particular processor or configuration requires. Refer to the *IBM Series/1 Configurator*, GA34-0042, for details about the requirements for the use of the repower feature.

IBM I/O attachment cards plug directly into the backpanel sockets. External I/O devices are connected to the attachment cards via top-card connectors.

Two features are available for connecting non-IBM devices directly to the channel: the channel socket adapter feature and the channel repower feature.

- Channel socket adapter feature—this feature consists of an IBM printed circuit card that plugs into the backpanel of the processor unit or I/O expansion unit. An industry-standard connector on the top edge of the IBM printed circuit card accepts the user's I/O adapter card. For further information, see "Socket Adapter Feature" in this chapter.

- Channel repower feature—this feature is a logic card that repowers

and isolates the channel signal lines. This card can be installed in any

I/O socket, as the last series element on the channel, to allow

connection of additional I/O adapters or controllers. For further

information, see "Channel Repower Feature" in this chapter.

If the user connects directly to the channel at the backpanel sockets instead of through one of the available features, the unit load, the power, and the physical requirements must be considered. These and other requirements are discussed in subsequent sections of this chapter.

**CAUTION:** To achieve adequate results, good design practices—both electrical and mechanical—must be adhered to. IBM bears *NO RESPONSIBILITY* for customer logic or hardware.

# Functional Description of I/O Channel Signal Lines

The I/O channel consists of 81 signal lines divided into two physical groups: the *service* group and the *poll* group. Each group can operate concurrently and asynchronously with the other group; however, the initiation of sequences on the channel is interdependent.

The service group supports:

- Data and control information transfers

- IPL initiation

- Reset functions

The poll group supports:

- Cycle-steal requests from the devices

- Interrupt requests from the devices

- Acknowlegement of both types of requests

### Signal Line Groups

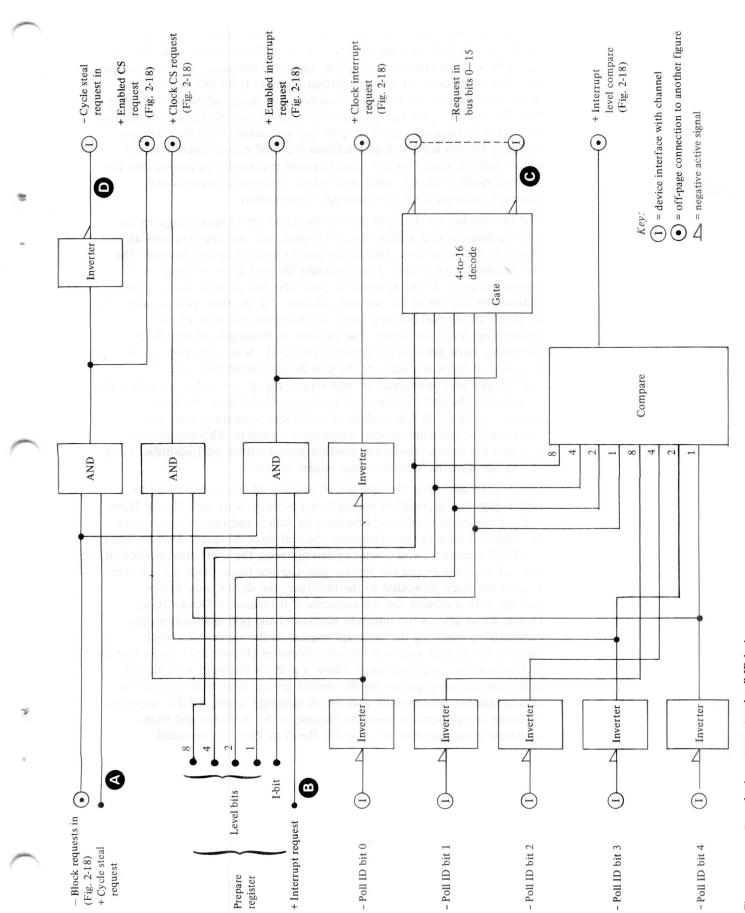

The I/O channel signal lines are shown, by group, in Figures 2-1 and 2-2.

Note: The direction is shown for each line with the assumption that the I/O channel originates on the left and the I/O attachments are on the right.

# Service Group Signal Lines

The signal lines associated with the service group are shown in Figure 2-1.

Figure 2-1. Service group signal lines

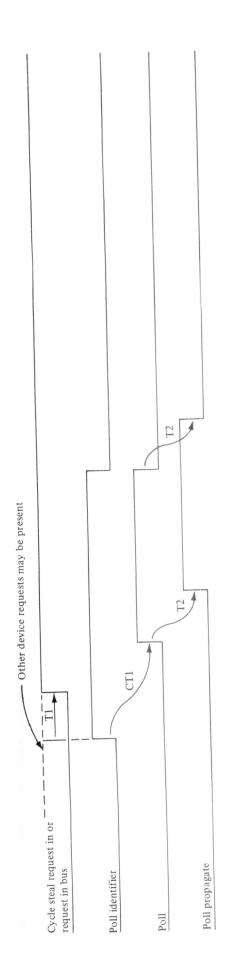

## Poll Group Signal Lines

The signal lines associated with the poll group are shown in Figure 2-2.

| Signal name            | Direction | Number of lines |

|------------------------|-----------|-----------------|

| Request in bus         | 4         | <b>-</b> 16     |

| Cycle steal request in | 4         | <b>-</b> 1      |

| Poll identifier        | -         | - 5             |

| Poll                   |           | <b>1</b>        |

| Poll prime             |           | <b>1</b>        |

| Poll propagate         | -         | <b>▶</b> 1      |

| Poll return            | -         | <b>-</b> 1      |

| Burst return           | 4         | _ 1             |

| Total number of lines  |           | 27              |

Figure 2-2. Poll group signal lines

## Functional Subsets of the Signal Lines

The I/O channel signal lines can have subsets, depending on the level of function required by the I/O attachment. In order of increasing level of function, these subsets are:

- Basic subset

- Interrupt subset

- Cycle-steal/IPL subset

Attachment to a subset is a prerequisite for attachment to the next higher level subset.

#### Basic Subset

The basic subset consists of the buses and tags to support functions initiated by the processor; for example, direct program control (DPC) commands. This includes the data transfers associated with the DPC command itself. The basic subset supports DPC devices that do not interrupt. I/O signal lines in the basic subset are shown in Figure 2-3.

## Service group signal lines

| Signal<br>name                 | Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Number of lines |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| Address bus bits 0-15 (Note 1) | CHARLOW WANTED TO STATE OF STA | 16              |  |

| Address bus bit 16             | CARLAMAN IN COLUMN STREET, STR | 1               |  |

| Data bus (Note 2)              | GENERALISM I I MONTHE STREET,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18              |  |

| Address gate                   | COMMUNICATION OF A PROPERTY OF THE PROPERTY OF | 1               |  |

| Address gate return            | - Comment of the state of the s | 1               |  |

| Condition code in bus          | Maria de la composition della  | 3               |  |

| Data strobe                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1               |  |

| Halt or MCHK                   | AND ADDRESS OF THE LAST OF T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1               |  |

| System reset                   | CONTRACTOR DE LE CONTRACTOR DE LA CONTRA | 1               |  |

| Power on reset                 | CONTRACTOR OF THE PROPERTY OF  | 1               |  |

| Poll group signal lines        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |  |

| Poll (Note 3)                  | AND ADDRESS OF THE PARTY OF THE | 1               |  |

| Poll prime (Note 3)            | AND DESCRIPTION OF THE OWNERS OF THE OWNERS OF THE OWNER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1               |  |

| Poll propagate (Note 3)        | - NORTH COMMON TO THE PROPERTY OF THE PROPERTY | 1               |  |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |  |

#### Notes:

- 1. Address bus bits 0-15 need only be received in this subset.

- 2. Bidirectional data bus capability is assumed for this subset; however, if the direction of data flow within a device is fixed (specifically, a read-only device attachment with no write or interrupt capability), the device need not implement bidirectional data drivers and receivers. In this case, the device must reject all commands requiring a transfer in other than the direction implemented by the device. For the interrupt subset (described in "Interrupt Subset" in this chapter), the device must implement bidirectional data bus drivers and receivers.

- 3. 'Poll' and "poll prime' need only be received, logically ANDed, and redriven on the 'poll propagate' line to maintain continuity of the serial poll mechanism. Any card installed on the channel, even though it does not operate on the channel, must propagate 'poll' and 'poll prime.'

Figure 2-3. Basic subset

# Interrupt Subset

The interrupt subset consists of control buses and tags to support an interrupting source on the I/O channel. This subset provides the means to: (1) present interrupt requests to the processor, (2) resolve contention, (3) acknowledge an interrupt, and (4) accept an interrupt.

The interrupt subset, in conjunction with the basic subset, supports DPC devices that are interrupting sources. The I/O signal lines in the interrupt subset are shown in Figure 2-4.

#### Service group signal lines Number Signal name Direction of lines Service gate 1 Service gate return Poll group signal lines Number Signal name Direction of lines Request in bus 16 Poll identifier 5 Poll 1 Poll prime 1 Poll propagate Poll return

Figure 2-4. Interrupt subset

# Cycle-Steal/IPL Subset

The cycle-steal/IPL subset consists of control buses and tags to support cycle-steal, burst transfer, and IPL operations. This subset provides the means to present cycle-steal requests to the processor, to resolve contention, and to service the cycle-steal transfers. The cycle-steal/IPL subset, in conjunction with the basic and the interrupt subsets, supports devices that cycle-steal and DPC devices capable of IPL. The I/O signal lines in the cycle-steal/IPL subset are shown in Figure 2-5.

## Service group signal lines Signal Number name Direction of lines Address bus bits 0-15 (Note 1) Cycle input indicator Cycle byte indicator Status bus Initiate IPL (Note 2) IPL (Note 2) Poll group signal lines Signal Number name Direction of lines Cycle steal request in Burst return (Note 3)

- 1. Address bits 0-15 must have full bidirectional capability for this subset.

- 2. Required only for devices supporting IPL. Initiate IPL is not required for devices that only support IPL from a host system.

- 3. Required only if burst cycle-steal transfers are supported by the device.

Figure 2-5. Cycle-steal/IPL subset

Notes:

## Service Group Line Definitions

Address Bus Bits 0-15. This is a 16-bit bidirectional bus that is received by all I/O devices. The bus is used on direct program control (DPC) sequences to select and pass commands to the I/O devices. On DPC sequences, address bus bits 0-15 are logically equal to the contents of bits 0-15 of the first word of the IDCB. The channel select bit (IDCB bit 0) on address bus bit 0 can be ignored for device selection.

The address bus is also used on cycle-stealing sequences to present main storage addresses to the channel controls. On cycle-steal service sequences, address bits 0-15, which are driven by the I/O device, correspond to storage address bits 0-15 of the data to be transferred.

Address bus bits 0–15 are not used on interrupt-service sequences.

Address Bus Bit 16. This bit is an outbound tag received by all I/O devices. When active, this tag signals a DPC sequence to the I/O devices. The receiver for this tag is always enabled.

Data Bus. This is an 18-bit bidirectional bus with 16 bits of data and two parity bits (odd parity by byte). The data bus transfers data and control information: (1) between the processor and the I/O devices on DPC and interrupt-service sequences, and (2) between cycle-stealing devices and main storage on cycle-steal service sequences.

On DPC write sequences, data bus bits 0-15 are logically equal to the contents of bits 16-31 (second word) of the IDCB. If a single byte is to be transferred to the device, the byte is transferred from bits 24-31 of the IDCB; bits 16-23 should all be 0's. DPC write sequences are specified by address bus bit 1 (IDCB bit 1) equal to a logical 1.

Parity is always maintained for both bytes of the data bus on DPC write sequences; however, certain relaxations of the requirement to check parity on both bytes are allowed if a DPC device is byte-oriented. A byte-oriented device is a DPC device that does not use bits 16-23 of the IDCB for any DPC write or control function as specified in bits 1-3 of the IDCB. In this case, the device does not need to examine or parity check data bus bits 0-7 on DPC write or control sequences. A device that uses bits 16-23 of the IDCB for at least one DPC write sequence is not a byte-oriented device. Cycle-stealing devices cannot be byte-oriented devices because they implement the start functions.

On DPC read sequences, data bus bits 0-15 are driven by the device, and correspond to bits 16-31 of the IDCB. If a single byte is to be transferred from the device, the byte is transferred on data bus bits 8-15 with data bus bits 0-7 equal to logical 0's. DPC read sequences are specified by address bus bit 1 (IDCB bit 1) equal to logical 0. Parity must be maintained on both bytes of the data bus on DPC read sequences.

On interrupt-service sequences, the data bus is used to pass the interrupt ID word to the processor. Data bus bits 0-15 are driven by the device, and correspond to bits 0-15 of the interrupt ID word. The first byte of the interrupt ID word (bits 0-7) is the interrupt information byte; the second byte (bits 8-15) is the device address of the device being serviced.

Parity must be maintained on both bytes of the data bus on interrupt service sequences.

On cycle-steal service sequences, the data bus bits have the following meanings:

- Output, word transfer—data bus bits 0-15 are logically equal to the contents of the word at the storage address presented by the device; this storage address must be even. The device indicates an output word transfer by presenting 'cycle input indicator' equal to logical 0 and 'cycle byte indicator' equal to logical 0.

- Input, word transfer—data bus bits 0-15 are driven by the device and correspond to the word to be placed at the storage address presented by the device; this storage address must be even. The device indicates an input word transfer by presenting 'cycle input indicator' equal to logical 1 and 'cycle byte indicator' equal to logical 0.

- Output, byte transfer—the main storage address presented by the device determines the alignment of the byte on the data bus. If the storage address is even, data bus bits 0-7 are logically equal to the contents of the byte at the storage address. If the storage address is odd, data bus bits 8-15 are logically equal to the contents of the byte at the storage address. The device indicates an output byte transfer by presenting 'cycle input indicator' equal to logical 0 and 'cycle byte indicator' equal to logical 1.

- Input, byte transfer—the device must align the byte on the data bus according to the storage address being presented. If the storage address is even, data bus bits 0-7 are driven by the device and correspond to the byte to be placed at the storage address. If the storage address is odd, data bus bits 8-15 are driven by the device and correspond to the byte to be placed at the storage address. The device indicates an input by presenting 'cycle input indicator' equal to logical 1 and 'cycle byte indicator' equal to logical 1.

The I/O architecture allows both byte and word cycle-steal data transfers during the execution of a given cycle-steal operation. For example, an operation transferring an even number of bytes into a data table on an odd storage boundary could transfer one byte, then a number of words, and then end with a byte transfer.

Parity is maintained on both bytes of the data bus during cycle-steal output transfers. I/O devices must check both bytes of the data bus regardless of whether a word or byte is being transferred. Parity must be maintained on both bytes of the data bus on cycle-steal input transfers.

During byte transfers, the channel or device must maintain a stable data bus and parity for purposes of parity checking by the receiver of the data. However, the logical value of the particular byte not being used does not have to be specified because it is parity checked only. For output byte transfers, the value of the unused byte may be different on each transfer and may be different among the Series/1 processors. For input byte transfers, most device attachments, as a matter of practice, have found it simplest to zero out the unused byte and force the parity bit accordingly.

Address Gate. This is an outbound tag used during DPC sequences. This tag signals a device that it can respond to initial selection and begin execution of the command specified by bits 0-7 of the address bus.

Address Gate Return. This is an inbound tag used by the selected device during a DPC sequence. This tag signals: (1) the reception of 'address gate,' (2) the activation of 'condition code in bus,' and (3) the activation of 'data bus' for a read sequence.

Service Gate. This outbound tag signals the device that last captured a poll that a cycle-steal or interrupt-service sequence can begin. The I/O device detects the leading edge of this tag following a poll capture to begin the sequence; this is called service gate capture.

Service Gate Return. This is an inbound tag used by a device to signal a service gate capture and activation of 'address bus' (on a cycle-steal sequence), 'data bus,' 'condition code in bus,' and other tags as required by the particular cycle-steal or interrupt-service sequence.

Condition Code In Bus. This is a three-bit, binary encoded inbound bus used by the I/O device on DPC, interrupt, and cycle-steal sequences.

On DPC and interrupt-service sequences, the 'condition code in bus' corresponds to the condition code indicators in the level status register (LSR) as follows:

| Condition   | LSR indicator |  |

|-------------|---------------|--|

| code in bit |               |  |

| 0           | Even          |  |

| 1           | Carry         |  |

| 2           | Overflow      |  |

On cycle-steal service sequences, the 'condition code in bus' is used by the device to pass the address key to the channel. On cycle-steal data transfers, condition code bits 0-2 are logically equal to the cycle-steal address key. This key is bits 5-7 of the DCB control word previously fetched by the device. During cycle-steal transfers for fetching the DCB and for reporting residual status, a value of logical 0 is used for the address key. During IPL cycle-steal transfers, a value of logical 0 is also used for the address key.

Cycle Input Indicator. This is an inbound tag used by the device on a cycle-steal service sequence. This tag signals the channel that the cycle-steal is either: (1) an output from storage or (2) an input to storage. When the indicator is a logical 0, an output from storage is indicated; when the indicator is a logical 1, an input to storage is indicated.

Cycle Byte Indicator. This is an inbound tag used by the device on a cycle-steal service sequence. This tag signals the channel that the cycle-steal is either: (1) a word transfer or (2) a byte transfer. When the indicator is a logical 0, a word transfer is indicated; when the indicator is a logical 1, a byte transfer is indicated.

**Status Bus.** This is an outbound four-bit bus used by the channel on a cycle-steal service sequence. The bus signals the device being serviced of any errors that the channel has detected. The bus is bit-significant, as follows:

| Status<br>bus bit | Meaning                 | IPL meaning      |

|-------------------|-------------------------|------------------|

| 0                 | Storage data check      | Primary device   |

| 1                 | Invalid storage address | Alternate device |

| 2                 | Protect check           |                  |

| 3                 | Interface data check    |                  |

If an error is indicated on cycle-steal service sequences that are not a part of IPL, the device retains this information for presentation to the software via ISB bits 4–7 at interruption time. Cycle-steal operations are terminated and an exception interrupt is presented. If an error is indicated on IPL cycle-steal sequences, the device terminates cycle-steal operations, but remains in an IPL state with the 'IPL' line active and does not present an end interrupt. Therefore, it is not necessary that status bus bits be recorded during IPL for later presentation. DPC devices supporting IPL should especially note this.

Bits 0 and 1 of the status bus are also used to select the primary and alternate IPL source, respectively. The appropriate bit of the status bus is activated with the 'initiate IPL' signal to accomplish this selection. Only one device can be configured as a primary IPL source and only one device can be configured as an alternate IPL source at any one time on the I/O channel attached to the processor.

Data Strobe. This is an outbound tag to the I/O device on: DPC, interrupt, or cycle-steal service sequences. This tag can be used by I/O devices to: (1) accomplish control actions, (2) register data on outbound transfers, and (3) accomplish appropriate data resets on inbound transfers. 'Data strobe' always occurs on normal DPC write, cycle-steal, and interrupt-service sequences. On DPC read sequences, 'data strobe' is not activated if the channel detects a parity error.

Initiate IPL. This is an outbound tag from the channel to the IPL source when the IPL is initiated by the processor Load key. The 'initiate IPL' tag is singular in nature and meaning, and signals the IPL source that the processor requires an IPL. The receiver for this tag is always enabled.

Bits 0 and 1 of the status bus are used for selecting the primary and

Bits 0 and 1 of the status bus are used for selecting the primary and alternate sources, respectively; see "Status Bus" in this section.

*IPL*. This is an inbound tag (1) from the IPL source, activated in response to the 'initiate IPL' tag or (2) from a host system, to signal the processor that the host is initiating an IPL action. The storage load itself takes place via the cycle-steal mechanism from the selected device or from the host system.

Halt or MCHK. This is an outbound tag received by all I/O devices. The tag means that either: (1) a Halt I/O command has been issued by the program or (2) a machine-check class interrupt (excluding a storage parity check) has occurred. When this tag is detected by an I/O device, the device must disable selection, block poll propagation, and clear any status, states, requests, interface control logic, and registers, with the following exceptions:

- Residual address

- Prepare level and I-bit

- DI, DO, AI, and AO settings

- Timer values

- Those registers not addressable by the software

- Two-channel switch operation monitors

The receiver for the 'halt or MCHK' tag is always enabled.

System Reset. This is an outbound tag received by all I/O devices. The tag is singular in nature and meaning. When the tag is detected, the I/O device must disable selection, block poll propagation, and clear any status, states, requests, registers, and interface control logic, with the following exceptions:

- Residual address

- DI, DO, AI, and AO settings

- Timer values

- Those registers not addressable by the software

During IPL sequences, one system reset has a unique function, as described in "Processor-Initiated IPL" under "Design Considerations for Operational Sequences" in this chapter.

The receiver for this tag is always enabled.

Power On Reset. This is an outbound control line from the power supply to all system components, and is activated on all power on/off sequences. While the line is active, all system components are held in a system reset state. The residual address; DI, DO, AI, and AO settings; timer values; and operation monitors are also reset. The receiver for this line is always enabled.

Each processor and I/O expansion unit on the I/O channel has a self-contained unit power-on reset. These power-on resets are not electrically connected among units.

# **Poll Group Line Definitions**

**Request In Bus.** This is a 16-bit inbound bus used by an I/O device to request an interrupt. Bits 0-15 of the 'request in bus' are used by I/O devices to request interrupts on levels 0-15, respectively. Only levels 0-3 are used on current processors. The level on which the device is to interrupt corresponds to the encoded value in the level field in the Prepare command.

Cycle Steal Request In. This is an inbound tag used by a cycle-stealing device when an access to storage is required.

**Poll Identifier.** This is a five-bit outbound bus used by the channel to indicate the nature of the poll presently being propagated to the I/O devices. 'Poll identifier' is always recognizable by I/O devices that are capable of cycle-stealing and/or presenting interrupts to the processor. The channel places a value on the poll identifier bus prior to raising the 'poll' tag and holds it valid until a 'poll return' or 'burst return' is received.

The significance of the poll identifier bits is as follows (poll ID bits are shown using logical representation for active/inactive):

| Poll            |                             |

|-----------------|-----------------------------|

| identifier bits | Meaning                     |

| 0 1 2 3 4       |                             |

| 0 0 0 0 0       | Poll for interrupt level 0  |

| 0 0 0 0 1       | Poll for interrupt level 1  |

| 0 0 0 1 0       | Poll for interrupt level 2  |

| 0 0 0 1 1       | Poll for interrupt level 3  |

| 0 0 1 0 0       | Poll for interrupt level 4  |

| 0 0 1 0 1       | Poll for interrupt level 5  |

| 0 0 1 1 0       | Poll for interrupt level 6  |

| 0 0 1 1 1       | Poll for interrupt level 7  |

| 0 1 0 0 0       | Poll for interrupt level 8  |

| 0 1 0 0 1       | Poll for interrupt level 9  |

| 0 1 0 1 0       | Poll for interrupt level 10 |

| 0 1 0 1 1       | Poll for interrupt level 11 |

| 0 1 1 0 0       | Poll for interrupt level 12 |

| 0 1 1 0 1       | Poll for interrupt level 13 |

| 0 1 1 1 0       | Poll for interrupt level 14 |

| 0 1 1 1 1       | Poll for interrupt level 15 |

| 1 0 0 0 0       | Quiescent value             |

| 1 0 1 0 0       | Reserved                    |

| 1 1 0 0 0       | Reserved                    |

| 1 1 1 0 0       | Reserved                    |

| 1 X X 0 1       | Reserved                    |

| 1 X X 1 0       | Reserved                    |

| 1 X X 1 1       | Poll for cycle-steal        |

The poll identifiers for interrupt levels 4–15 are not used on current processors.

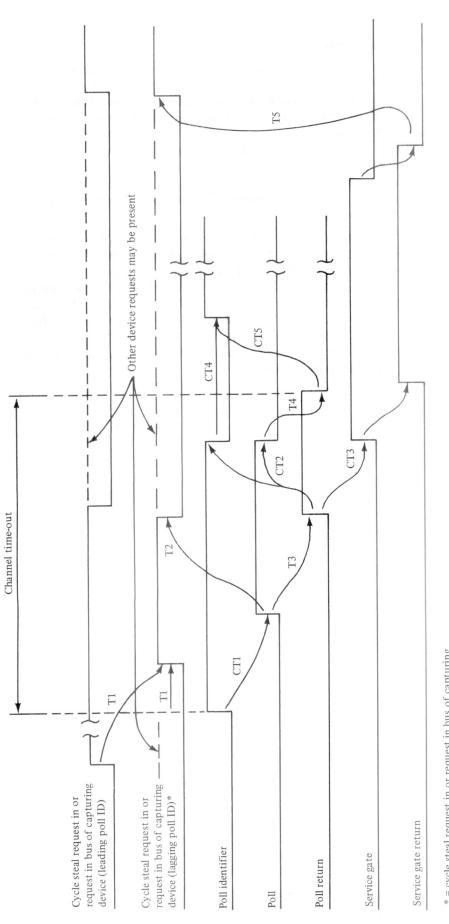

Poll and Poll Prime. The 'poll' tag is a serially propagated tag generated by the channel to resolve contention between multiple devices requesting interruptions on the same level and cycle-steal requests. Each I/O device receives the 'poll' tag and redrives it to the next device on the I/O channel via its 'poll propagate' output line.

The 'poll' and 'poll prime' tags are always recognizable by an I/O device that is capable of presenting interrupts or cycle-stealing. An I/O device recognizes a poll as the leading edge of the logical AND of 'poll' and 'poll prime.' The device does a logical compare between the poll ID bits on the interface and the ID bits in its prepare register. An equal compare of the poll ID Bits ANDed with 'poll' and 'poll prime' is called poll capture. Once the poll is captured, an I/O device can then respond with 'poll return' or 'burst return.' If the poll capture does not occur, the 'poll' tag is propagated to the next device on the I/O channel.

Because of the serial nature of the poll mechanism, the relative physical position of I/O attachments on the channel is a major determinant of the priority for servicing contending cycle-steal requests and for servicing contending interrupt requests on the same interrupt level. Those attachments located in positions nearer to the processor are the first elements on the serial poll chain and are effectively of higher priority.

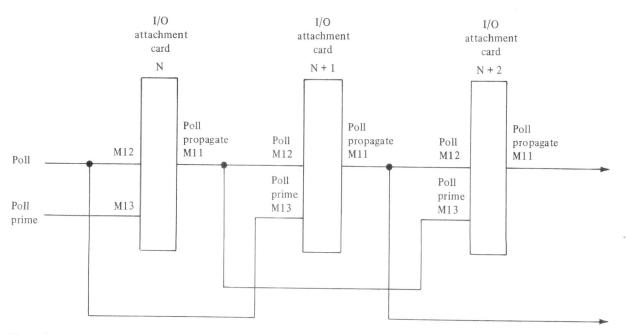

To facilitate the removal of an I/O attachment card from the I/O channel without interrupting the poll propagation, a bypass mechanism is provided (refer to Figure 2-6). The 'poll prime' tag received by I/O attachment card N+2 is the same line that I/O attachment card N+1 receives as its 'poll' tag. If I/O attachment card N is removed, the 'poll' tag input to attachment card N+1 and the 'poll prime' input to attachment card N+2 appear as a logical 1. The 'poll prime' input to attachment card N+1 then follows the 'poll propagate' output of attachment card N-1.

Figure 2-6. Poll bypass mechanism

If an I/O device does not present interrupt or cycle-steal requests, the 'poll' and 'poll prime' tags are received, logically ANDed, and then redriven to the 'poll propagate' output. Cards that use an I/O slot on the channel, but are never logically connected to the channel as a device attachment, must also implement this logical ANDing and redrive capability.

### Notes:

- 1. The poll bypass function applies on and between the processor and I/O expansion units.

- The cable slots and repower card are not considered to be an I/O attachment for purposes of the poll bypass mechanism (it is not permissible to leave an empty I/O slot on each side of the repower card).

**Poll Propagate.** This outbound tag is sent by an I/O device when it receives a poll that it has not captured.

**Poll Return.** This is an inbound tag sent by an I/O device to signal the channel that a poll capture for an interrupt poll or for a non-burst cycle-steal service poll has taken place. It is not used to signify that a burst transfer is required.

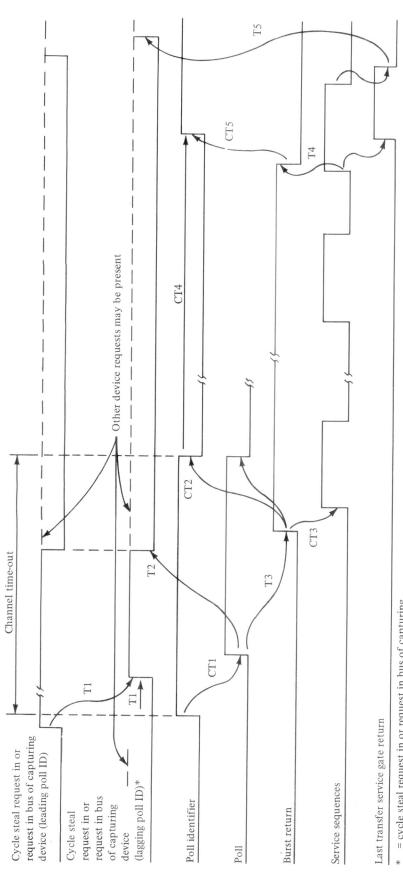

Burst Return. This is an inbound tag sent by an I/O device to signal the channel that a poll capture (cycle-steal only) has taken place and that a burst transfer is required. Once 'burst return' is activated, the next leading edge of a 'service gate' tag signals the beginning of the burst transfer. During the burst operation, all other channel-attached devices are precluded from using the channel. 'Service gate'/'service gate return' 'handshaking," between the channel and the I/O device, continues until the 'burst return' tag is dropped. An I/O device deactivates the 'burst return' tag at the rise of the 'service gate' tag for the last transfer. Under program control, burst mode is used only if so specified in the DCB control word. A device capable of supporting burst mode must also be capable of non-burst operations. (DCB fetching is always done in non-burst mode.) Burst mode is not precluded for IPL transfers.

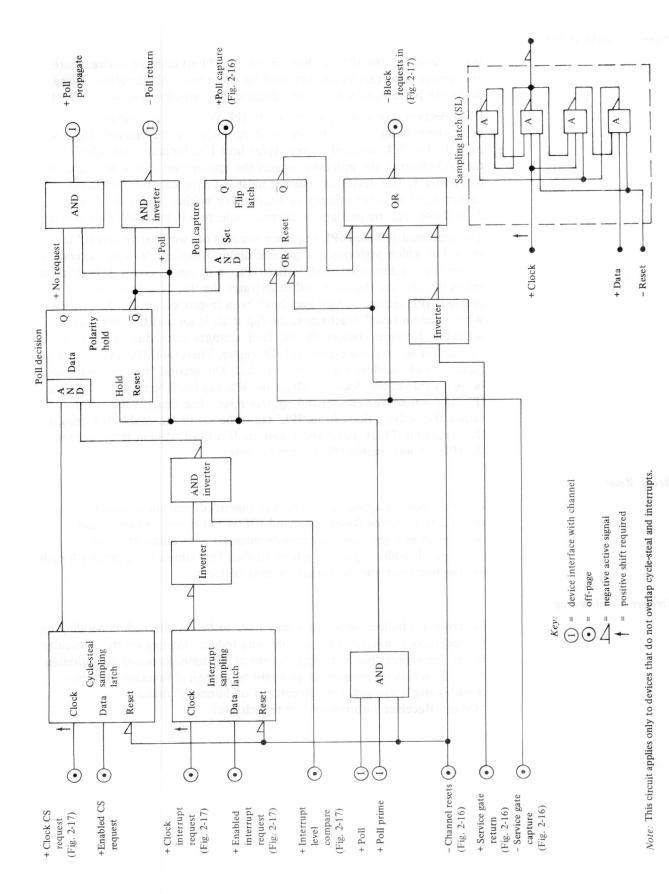

# Processor I/O Channel Operational Characteristics

# Operational Sequences on the Channel

Operations on the processor I/O channel are performed by the following major signal sequences, utilizing either the service group, the poll group, or a combination of both:

- DPC sequence (service group)—a write or read transfer initiated by an Operate I/O instruction. The sequence terminates after one byte or one word is transferred.

- Interrupt-service sequence (service group)—initiated by a poll capture following an interrupt request from an I/O device. The sequence is terminated after the interrupt ID word is transferred.

- Cycle-steal service sequence (service group)—an input or output transfer initiated by a poll capture after a cycle-steal request from the I/O device. The sequence terminates after one byte- or word-transfer unless burst mode is active.

- Poll sequence (poll group)—initiated by either an interrupt request or a cycle-steal request. The poll is either propagated or captured by an I/O device. If the poll is captured, the I/O device returns a 'poll return' tag to indicate either (1) the capture of an interrupt poll or (2) a single cycle-steal transfer. The device returns the 'burst return' tag for multiple cycle-steal transfers.

- Processor-initiated IPL sequence (service and poll group)—initiated when the Load key on the console is pressed. The sequence terminates when the I/O device has transferred the complete IPL record.

- Host-initiated IPL sequence (service and poll groups)—initiated by a signal from the I/O attachment that connects the I/O channel to the host processor. The sequence terminates when the complete IPL record has been transferred.

- Reset sequences—(1) initiated by the 'halt or MCHK' tag when a Halt I/O command is issued or when a machine-check interrupt occurs, or (2) initiated when the system Reset key on the console is pressed.

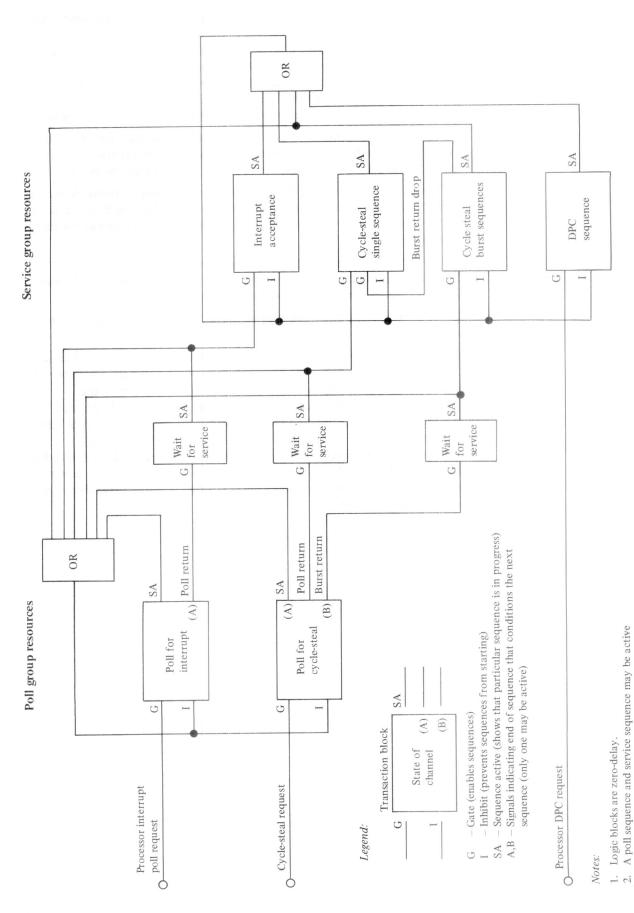

The service and poll groups operate concurrently and asynchronously to each other. This characteristic is a major operational and design consideration. However, some of the sequences occurring on the I/O channel are interdependent. Figure 2-7 is a block diagram illustrating the architectural interdependencies of the major channel sequences from the viewpoint of a group of devices in normal operation. This diagram does not attempt to show contention resolution in the channel or provide a system level description. The IPL and reset sequences are of a special nature. IPL sequences use the poll and service groups in combination and involve operations with only one specific device and with no other device active. Resets are entirely asynchronous and affect operations on both groups.

The inputs on the left side of the diagram are:

- A processor interrupt poll request and a cycle-steal request to the poll group. The processor generates a request for an interrupt poll only after the priority interrupt algorithm is satisfied and the processor can accept the interrupt. The cycle-steal request is generated by I/O devices on the channel itself.

- 2. A processor DPC request to the service group, which is done inline with the execution of an Operate I/O instruction.

Although the poll group and service group resources can be active simultaneously, each group can have only one of its possible transactions active at a time. Therefore, the inputs (requests) to each group must be mutually exclusive at the instant in time the group becomes free to gate another transaction. If the sources of the inputs are running asynchronously, then contention among the requests must be resolved. Although input relationships and contention resolutions are not shown in the diagram, the following can be assumed:

- The processor interrupt poll request and the processor DPC requests are mutually exclusive. This occurs because the processor cannot perform priority interrupt acceptance and execute an Operate I/O instruction at the same time.

- Contention is resolved between processor interrupt poll and cycle-steal requests at the input to the poll group at the time the poll group becomes free to gate another transaction.

- Contention is resolved between processor DPC and poll group requests at the input to the service group at the time the service group becomes free to gate another transaction block.

For example, assume that a processor interrupt poll request becomes active and is gated into the "poll for interrupt" block. This starts the polling sequence. When the poll for interrupt sequence is complete, the poll group resource is waiting for the service group. When the service group becomes available, the interrupt acceptance block is gated, thus tying up the service group. However, as soon as the interrupt acceptance block is gated, the poll group is free to do further polling concurrent with the service group.

As another example, assume that the cycle-steal burst sequence is active. Figure 2-7 shows that this sequence degates all other sequences. Note also that the last sequence of a burst operation enables concurrent polling.

Each major sequence is described in subsequent sections. Timing diagrams are used to show the important timing relationships that the designer needs to adhere to (or be aware of) when designing an I/O attachment for the I/O channel.

The designer has no control over, but must be aware of, channel times (CT). The designer does have control of the attachment-controlled times (T-times), because these are considered dependent times.

The diagrams use the convention of an up level to denote an active tag or a valid bus value.

The designer should ensure that the signals presented to the I/O channel meet the specified T-times, as shown on the timing diagrams. Because the designer does not control the loading, as seen at the output of the interface drivers in a given configuration, these timings should be met, assuming the maximum loading permissible for the particular drivers being used. There are cases where differences in driver delays must be considered. For example, certain signals must be deactivated prior to a tag being dropped at the device adapter interface. In such cases, one driver can be considered at nominal delay and the other at worst-case delay, with both at maximum load.

Figure 2-7. Channel sequence interdependencies

simultaneously, when allowed.

## **DPC Sequence Description**

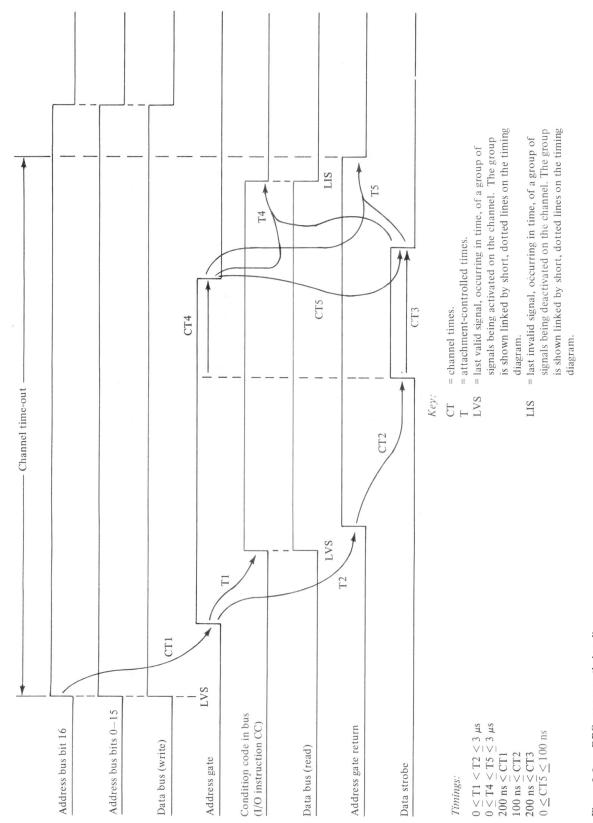

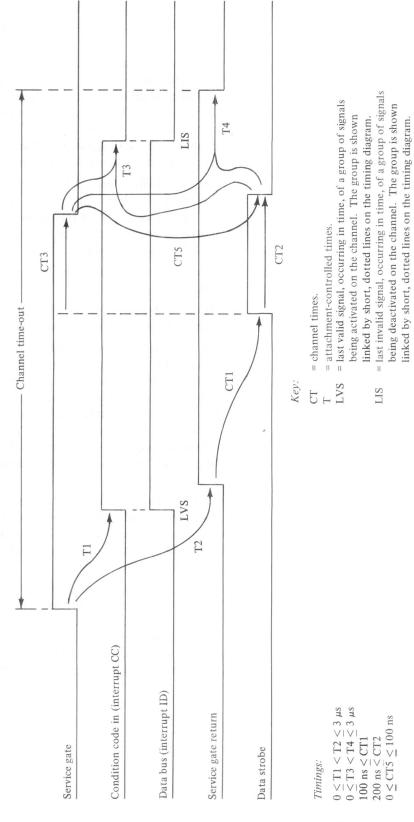

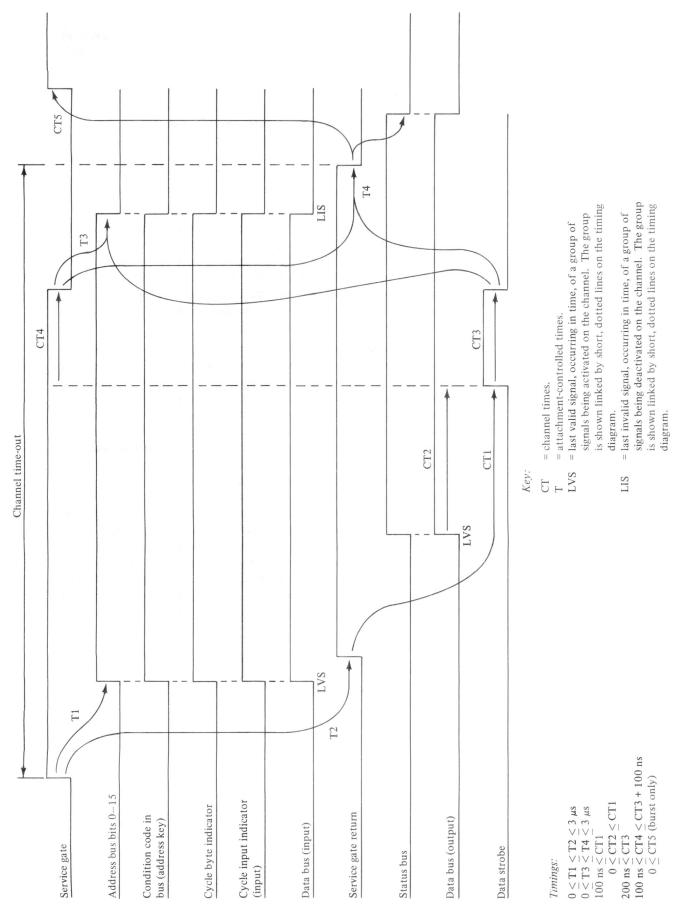

Refer to Figure 2-8. DPC write and DPC read sequences are executed as follows:

1. 'Address bus bits 0-15' and 'address bus bit 16' (and 'data bus' on write sequences) are activated by the channel. These buses are held valid until the fall of 'address gate return,' as seen at the processor channel input.

The activation of address bus bit 16 causes all I/O attachments to compare address bus bits 8-15 (the device address) with the attachment's assigned device address(es). An equal comparison constitutes DPC selection of the device. Upon selection, the device examines the command in address bus bits 0-7 (and the data bus, for proper parity on write sequences), and applicable device internal conditions necessary for determining command acceptance and I/O instruction condition code reporting. No specific device action or state change must occur as a result of the selection and examination of conditions relative to the command itself until: (1) 'address gate' is recognized by the selected device for write sequences, or (2) 'data strobe' is recognized by the selected device for read sequences. For write sequences, the device should not change state until 'data strobe' is recognized, except during execution of a Device Reset command. If an I/O device has an interrupt request active on the interface and executes a Device Reset or Prepare command, the device, as appropriate, drops its request or alters its requested level prior to the deactivation of 'data strobe,' as seen at the device interface.

2. 'Address gate' is deskewed and activated on the channel. The deskew time, CT1, between the last valid signal of 'address bus' (and 'data bus' on write sequences) and the activation of 'address gate,' measured at the device interface, is 200 nanoseconds, minimum. Upon recognition of the 'address gate' by the selected device, the device activates the 'condition code in bus' (and the 'data bus' on read sequences) and then activates 'address gate return.'

The 'condition code in bus' (and 'data bus' on read sequences) must be activated prior to 'address gate return,' as seen at the device interface. These buses must be held valid and must not change in value until the deactivation of 'address gate' and 'data strobe' at the device interface.